ఇప్పటివరకు మేము BJT విశ్లేషణను వాటి స్థాయికి పైగా β స్థాయిని బట్టి అధ్యయనం చేస్తున్నాము ఆపరేటింగ్ పాయింట్లు (Q- పాయింట్) . ఆపరేటింగ్ పాయింట్లు లేదా క్యూ-పాయింట్ల యొక్క సాధ్యమైన పరిధిని నిర్ణయించడంలో మరియు వాస్తవ క్యూ-పాయింట్ను స్థాపించడంలో ఇచ్చిన సర్క్యూట్ పరిస్థితులు ఎలా సహాయపడతాయో ఈ చర్చలో మేము పరిశీలిస్తాము.

లోడ్ లైన్ విశ్లేషణ అంటే ఏమిటి

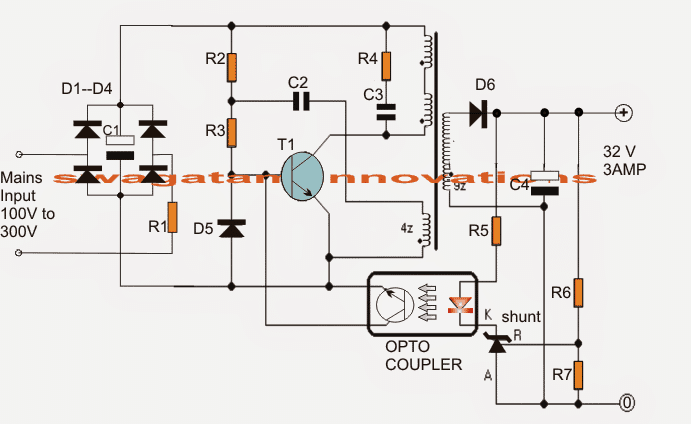

ఏదైనా ఎలక్ట్రానిక్ వ్యవస్థలో సెమీకండక్టర్ పరికరంలో వర్తించే లోడ్ సాధారణంగా ఆపరేషన్ పాయింట్ లేదా పరికరం యొక్క ఆపరేషన్ ప్రాంతంపై గణనీయమైన ప్రభావాన్ని చూపుతుంది.

గ్రాఫ్ డ్రాయింగ్ ద్వారా ఒక విశ్లేషణ జరిగితే, అనువర్తిత లోడ్ను స్థాపించడానికి పరికరం యొక్క లక్షణాలలో మేము సరళ రేఖను గీయగలుగుతాము. పరికరం యొక్క లక్షణాలతో లోడ్ లైన్ యొక్క ఖండన ఆపరేషన్ పాయింట్ లేదా పరికరం యొక్క Q- పాయింట్ను నిర్ణయించడానికి ఉపయోగించవచ్చు. ఈ విధమైన విశ్లేషణ, స్పష్టమైన కారణాల వల్ల, లోడ్-లైన్ విశ్లేషణ అంటారు.

లోడ్ లైన్ విశ్లేషణను ఎలా అమలు చేయాలి

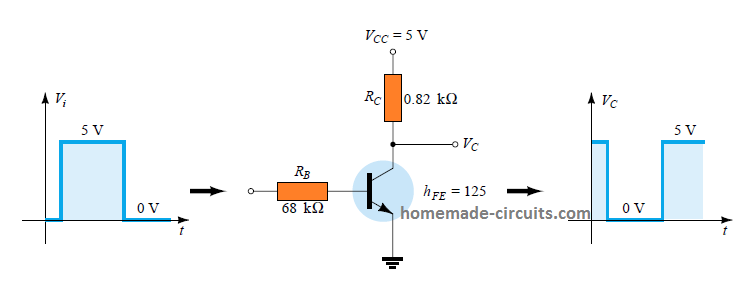

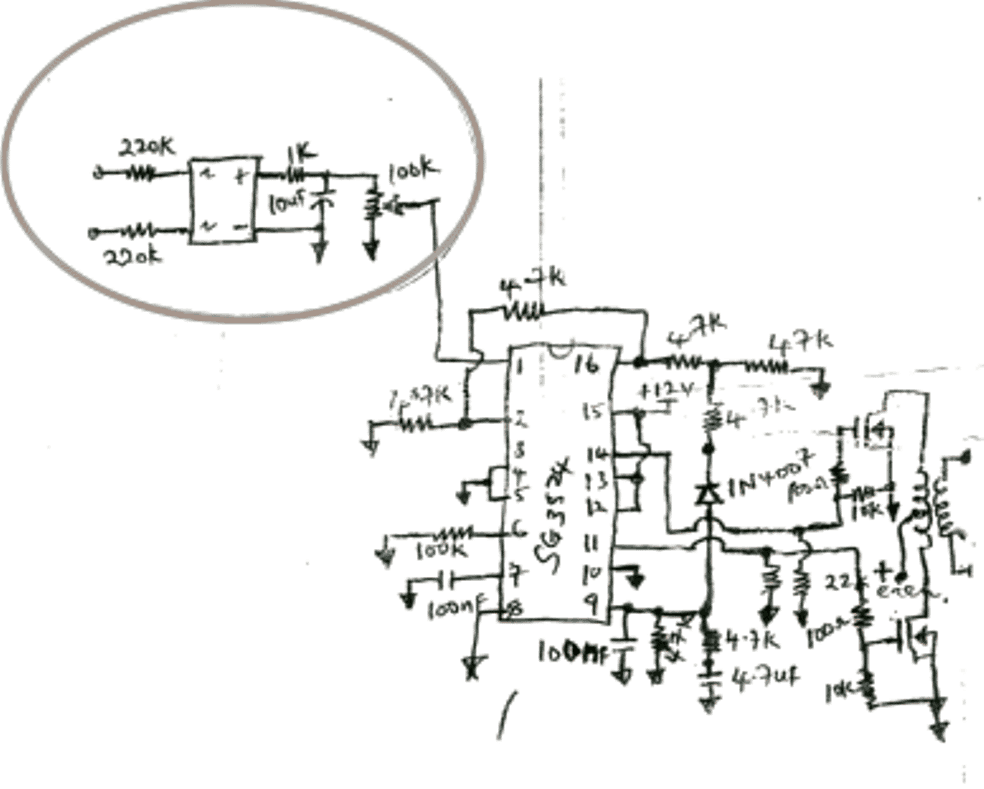

కింది అంజీర్ 4.11 (ఎ) లో చూపిన సర్క్యూట్ అవుట్పుట్ సమీకరణాన్ని నిర్ణయిస్తుంది, ఇది క్రింద చూపిన విధంగా వేరియబుల్స్ IC మరియు VCE ల మధ్య సంబంధాన్ని అందిస్తుంది:

VCE = VCC - ICRC (4.12)

ప్రత్యామ్నాయంగా, పైన ఉన్న రేఖాచిత్రం (బి) లో చూపిన విధంగా ట్రాన్సిస్టర్ యొక్క అవుట్పుట్ లక్షణాలు కూడా IC మరియు VCE అనే రెండు వేరియబుల్స్ మధ్య సంబంధాన్ని అందిస్తాయి.

సారూప్య వేరియబుల్స్తో పనిచేసే గ్రాఫికల్ ప్రాతినిధ్యం ద్వారా సర్క్యూట్ రేఖాచిత్రం ఆధారిత సమీకరణం మరియు లక్షణాల శ్రేణిని పొందడానికి ఇది మాకు సహాయపడుతుంది.

వాటి ద్వారా నిర్వచించబడిన అడ్డంకులు ఏకకాలంలో నెరవేరినప్పుడు రెండింటి నుండి సాధారణ ఫలితం ఏర్పడుతుంది.

ప్రత్యామ్నాయంగా ఇది రెండు ఉమ్మడి సమీకరణాల నుండి సాధించిన పరిష్కారాలుగా అర్థం చేసుకోవచ్చు, ఇక్కడ ఒకటి సర్క్యూట్ రేఖాచిత్రం సహాయంతో ఏర్పాటు చేయబడుతుంది, మరొకటి BJT డేటాషీట్ లక్షణాల నుండి.

Fig. 4.11b లో, BJT యొక్క IC vs VCE లక్షణాలను మనం చూడవచ్చు, కాబట్టి ఇప్పుడు మనం లక్షణాలపై Eq (4.12) వివరించిన సరళ రేఖను అతిశయోక్తి చేయగలుగుతున్నాము.

లక్షణాలపై Eq (4.12) ను కనిపెట్టడానికి సులభమైన పద్ధతి నియమం ద్వారా అమలు చేయవచ్చు, ఇది ఏదైనా సరళ రేఖను రెండు విభిన్న బిందువుల ద్వారా నిర్ణయిస్తుందని చెబుతుంది.

IC = 0mA ని ఎంచుకోవడం ద్వారా, క్షితిజ సమాంతర అక్షం ఒక బిందువు దాని స్థానాన్ని తీసుకునే రేఖగా మారుతుంది.

IC = 0mA ని Eq (4.12) లో భర్తీ చేయడం ద్వారా మనకు లభిస్తుంది:

దిగువ అత్తి 4.12 లో సూచించిన విధంగా ఇది సరళ రేఖకు ఒక పాయింట్ను నిర్ణయిస్తుంది:

ఇప్పుడు మనం VCE = 0V ని ఎంచుకుంటే, ఇది నిలువు అక్షాన్ని మన రెండవ బిందువు దాని స్థానాన్ని తీసుకునే పంక్తిగా సెట్ చేస్తుంది. ఈ పరిస్థితులతో, కింది సమీకరణం ద్వారా IC ని అంచనా వేయవచ్చని ఇప్పుడు మనం కనుగొనగలిగాము.

ఇది అంజీర్ 4.12 లో స్పష్టంగా చూడవచ్చు.

Eqs నిర్ణయించిన విధంగా రెండు పాయింట్లను కనెక్ట్ చేయడం ద్వారా. (4.13) మరియు (4.14), Eq 4.12 చేత స్థాపించబడిన సరళ రేఖను గీయవచ్చు.

అంజీర్ 4.12 గ్రాఫ్లో చూసినట్లుగా ఈ పంక్తి గుర్తించబడింది లోడ్ లైన్ ఎందుకంటే ఇది లోడ్ రెసిస్టర్ RC ద్వారా వర్గీకరించబడుతుంది.

IB యొక్క స్థిర స్థాయిని పరిష్కరించడం ద్వారా, అంజీర్ 4.12 లో చూపిన విధంగా వాస్తవ Q- పాయింట్ను పరిష్కరించవచ్చు

మేము RB విలువను మార్చడం ద్వారా IB యొక్క పరిమాణాన్ని మారుస్తే, అంజీర్ 4.13 లో చూపిన విధంగా Q- పాయింట్ లోడ్ రేఖకు పైకి లేదా క్రిందికి మారుతుంది.

మేము స్థిరమైన VCC ని నిర్వహిస్తే, మరియు RC యొక్క విలువను మాత్రమే మార్చుకుంటే, అంజీర్ 4.14 లో సూచించిన విధంగా లోడ్ లైన్ బదిలీ అవుతుందని మేము కనుగొన్నాము.

మేము IB ని స్థిరంగా ఉంచినట్లయితే, Q- పాయింట్ దాని స్థానాన్ని అదే బొమ్మ 4.14 లో సూచించినట్లుగా మారుస్తుందని మేము కనుగొన్నాము .మరియు RC ని స్థిరంగా ఉంచి, VCC మాత్రమే మారుతూ ఉంటే, అంజీర్ 4.15 లో వర్ణించిన విధంగా లోడ్ లైన్ కదులుతున్నట్లు మనం చూస్తాము

ప్రాక్టికల్ లోడ్ లైన్ విశ్లేషణ ఉదాహరణను పరిష్కరించడం

సూచన: https://en.wikipedia.org/wiki/Load_line_(electronics)

మునుపటి: లీనియర్ ఫస్ట్-ఆర్డర్ డిఫరెన్షియల్ ఈక్వేషన్స్ ఉపయోగించి ఓం యొక్క లా / కిర్చోఫ్ యొక్క చట్టం తర్వాత: ఉద్గారిణి-స్థిరీకరించిన BJT బయాస్ సర్క్యూట్