ప్రస్తుతం ఉన్న రెండు ప్రధాన రకాల FET లు: JFET లు మరియు MOSFET లు.

MOSFET లను మరింత క్షీణత రకంగా వర్గీకరించవచ్చు మరియు మెరుగుదల రకం. ఈ రెండు రకాలు MOSFET ల యొక్క ప్రాథమిక ఆపరేషన్ విధానాన్ని నిర్వచించాయి, అయితే MOSFET అనే పదం మెటల్-ఆక్సైడ్-సెమీకండక్టర్-ఫీల్డ్-ఎఫెక్ట్ ట్రాన్సిస్టర్ యొక్క సంక్షిప్తీకరణ.

రెండు రకాలు వేర్వేరు పని లక్షణాలను కలిగి ఉన్నందున, వాటిలో ప్రతి ఒక్కటి వేర్వేరు వ్యాసాలలో విడిగా అంచనా వేస్తాము.

వృద్ధి మరియు క్షీణత MOSFET మధ్య వ్యత్యాసం

ప్రాథమికంగా, మెరుగుదల MOSFET ల మాదిరిగా కాకుండా, గేట్-టు-సోర్స్ టెర్మినల్స్ (VGS) అంతటా 0 V సమక్షంలో కూడా క్షీణత MOSFET లు ఆన్-స్టేట్లో ఉంటాయి.

విస్తరణ MOSFET కోసం, గేట్-టు-సోర్స్ వోల్టేజ్ (VGS) దాని గేట్-టు-సోర్స్ థ్రెషోల్డ్ వోల్టేజ్ (VGS (వ)) పైన ఉండాలి అది నిర్వహించడానికి .

అయినప్పటికీ, N- ఛానల్ క్షీణత MOSFET కొరకు, దాని VGS (వ) విలువ 0 V కన్నా ఎక్కువ. దీని అర్థం VGS = 0 V అయినప్పటికీ, క్షీణత MOSFET ప్రస్తుతమును నిర్వహించగలదు. దాన్ని ఆపివేయడానికి, క్షీణత MOSFET యొక్క VGS ను VGS (వ) (ప్రతికూల) కంటే తగ్గించాలి.

ఈ ప్రస్తుత వ్యాసంలో మేము క్షీణత రకం MOSFET గురించి చర్చిస్తాము, ఇవి JFET యొక్క లక్షణాలతో సరిపోయే లక్షణాలను కలిగి ఉంటాయి. I దగ్గర కట్-ఆఫ్ మరియు సంతృప్తత మధ్య సారూప్యత ఉందిడిఎస్ఎస్.

ప్రాథమిక నిర్మాణం

Fig.5.23 n- ఛానల్ క్షీణత-రకం MOSFET యొక్క ప్రాథమిక అంతర్గత నిర్మాణాన్ని చూపిస్తుంది.

సిలికాన్ బేస్ ఉపయోగించి సృష్టించబడిన పి-టైప్ మెటీరియల్ యొక్క బ్లాక్ను మనం కనుగొనవచ్చు. ఈ బ్లాక్ను సబ్స్ట్రేట్ అంటారు.

MOSFET నిర్మించిన ఆధారం లేదా పునాది. కొన్ని MOSFET లకు ఇది అంతర్గతంగా 'సోర్స్' టెర్మినల్తో అనుసంధానించబడి ఉంది. అలాగే, అనేక పరికరాలు SS రూపంలో అదనపు ఉత్పత్తిని అందిస్తాయి, ఇందులో 4-టెర్మినల్ MOSFET ఉంటుంది, ఇది Fig.5.23 లో వెల్లడించింది

కాలువ మరియు సోర్స్ టెర్మినల్స్ వాహక పరిచయాల ద్వారా n- డోప్డ్ స్థానాలకు అనుసంధానించబడి, అదే చిత్రంలో సూచించిన విధంగా n- ఛానల్ ద్వారా జతచేయబడతాయి.

గేట్ ఒక లోహ పొరతో అనుసంధానించబడి ఉంది, అయినప్పటికీ ఇది సి-సి-డయాక్సైడ్ (SiO) యొక్క చక్కటి పొర ద్వారా n- ఛానల్ నుండి ఇన్సులేట్ చేయబడింది.రెండు).

SiOరెండుడైలెక్ట్రిక్ అని పిలువబడే ఒక ప్రత్యేకమైన ఇన్సులేషన్ ఆస్తి కలిగి ఉంది, ఇది బాహ్యంగా వర్తించే విద్యుత్ క్షేత్రానికి ప్రతిస్పందనగా తనలోనే ఒక వ్యతిరేక విద్యుత్ క్షేత్రాన్ని సృష్టిస్తుంది.

ఇన్సులేటింగ్ పొర కావడం, పదార్థం SiOరెండుకింది ముఖ్యమైన సమాచారాన్ని మాకు అందిస్తుంది:

ఈ పదార్థంతో గేట్ టెర్మినల్ మరియు మోస్ఫెట్ ఛానల్ మధ్య పూర్తి ఒంటరిగా అభివృద్ధి చేయబడింది.

అంతేకాక, దీనికి కారణం SiOరెండు, మోస్ఫెట్ యొక్క గేట్ ఇన్పుట్ ఇంపెడెన్స్ యొక్క అధిక స్థాయిని కలిగి ఉంటుంది.

ఈ కీలకమైన అధిక ఇన్పుట్ ఇంపెడెన్స్ ఆస్తి కారణంగా, గేట్ కరెంట్ I.జిఏదైనా dc- పక్షపాత MOSFET కాన్ఫిగరేషన్ కోసం వాస్తవంగా సున్నా ఆంప్స్.

ప్రాథమిక ఆపరేషన్ మరియు లక్షణాలు

AS ను Fig.5.24 లో చూడవచ్చు, గేట్ టు సోర్స్ వోల్టేజ్ రెండు టెర్మినల్స్ను అనుసంధానించడం ద్వారా సున్నా వోల్ట్ల వద్ద కాన్ఫిగర్ చేయబడింది, వోల్టేజ్ Vడి.ఎస్కాలువ మరియు మూల టెర్మినల్స్ అంతటా వర్తించబడుతుంది.

పై అమరికతో, JFET ఛానల్ ద్వారా సమానమైన ప్రవాహంతో పాటు, n- ఛానల్ ఉచిత ఎలక్ట్రాన్ల ద్వారా కాలువ వైపు సానుకూల సామర్థ్యాన్ని ఏర్పరుస్తుంది. అలాగే, ఫలితంగా ప్రస్తుత V.జి.ఎస్= 0 వి ఇప్పటికీ నేనుగా గుర్తించబడుతున్నానుడిఎస్ఎస్, అంజీర్ 5.25 లో ఇచ్చినట్లు

Fig.5.26 లో గేట్ సోర్స్ వోల్టేజ్ V.జి.ఎస్-1V రూపంలో ప్రతికూల సామర్థ్యాన్ని ఇస్తారు.

ఈ ప్రతికూల సంభావ్యత ఎలక్ట్రాన్లను పి-ఛానల్ సబ్స్ట్రేట్ వైపు బలవంతం చేయడానికి ప్రయత్నిస్తుంది (ఛార్జీలు తిప్పికొట్టడం వలన), మరియు పి-ఛానల్ సబ్స్ట్రేట్ నుండి రంధ్రాలను లాగండి (వ్యతిరేక ఛార్జీలు ఆకర్షిస్తాయి కాబట్టి).

ఈ ప్రతికూల పక్షపాతం ఎంత పెద్దది అనే దానిపై ఆధారపడి ఉంటుందిజి.ఎస్అంటే, రంధ్రాలు మరియు ఎలక్ట్రాన్ల పున omb సంయోగం జరుగుతుంది, దీని ఫలితంగా ప్రసరణకు అందుబాటులో ఉన్న n- ఛానెల్లో ఉచిత ఎలక్ట్రాన్లు తగ్గుతాయి. ప్రతికూల బయాస్ యొక్క అధిక స్థాయిలు పున omb సంయోగం యొక్క అధిక రేటుకు కారణమవుతాయి.

పైన పేర్కొన్న ప్రతికూల బయాస్ పరిస్థితి పెరిగినందున కాలువ ప్రవాహం తగ్గుతుంది, ఇది V కోసం Fig.5.25 లో నిరూపించబడిందిజి.ఎస్V స్థాయిలుజి.ఎస్= -1, -2 మరియు మొదలగునవి, -6 వి యొక్క చిటికెడు-ఆఫ్ గుర్తు వరకు.

ట్రాన్స్ఫర్ కర్వ్ ప్లాట్తో పాటు కాలువ ప్రవాహం a JFET.

ఇప్పుడు, సానుకూల V కోసంజి.ఎస్విలువలు, రివర్స్ లీకేజ్ కరెంట్ కారణంగా, గేట్ పాజిటివ్ p- రకం ఉపరితలం నుండి అదనపు ఎలక్ట్రాన్లను (ఉచిత క్యారియర్లు) ఆకర్షిస్తుంది. ఇది వేగవంతమైన కణాల అంతటా గుద్దుకోవటం ద్వారా తాజా క్యారియర్లను ఏర్పాటు చేస్తుంది.

గేట్-టు-సోర్స్ వోల్టేజ్ సానుకూల రేటుతో పెరిగే అవకాశం ఉన్నందున, కాలువ ప్రవాహం వేగంగా పెరిగినట్లు చూపిస్తుంది, పైన చర్చించిన అదే కారణాల వల్ల Fig.5.25 లో నిరూపించబడింది.

V యొక్క వక్రాల మధ్య అంతరం అభివృద్ధి చెందిందిజి.ఎస్= 0 వి మరియు విజి.ఎస్V యొక్క 1 - V వైవిధ్యం కారణంగా ప్రస్తుతము పెరిగిన మొత్తాన్ని = +1 స్పష్టంగా చూపిస్తుందిజి.ఎస్

కాలువ ప్రవాహం వేగంగా పెరగడం వల్ల మనం గరిష్ట ప్రస్తుత రేటింగ్ గురించి జాగ్రత్తగా ఉండాలి, లేకుంటే అది సానుకూల గేట్ వోల్టేజ్ పరిమితిని దాటవచ్చు.

ఉదాహరణకు, Fig.5.25 లో వర్ణించబడిన పరికర రకం కోసం, V ని వర్తింపజేస్తుందిజి.ఎస్= + 4V కాలువ ప్రవాహం 22.2 mA వద్ద పెరగడానికి కారణమవుతుంది, ఇది పరికరం యొక్క గరిష్ట విచ్ఛిన్న పరిమితిని (ప్రస్తుత) దాటవచ్చు.

పాజిటివ్ గేట్-టు-సోర్స్ వోల్టేజ్ యొక్క ఉపయోగం ఛానెల్లోని ఉచిత క్యారియర్ల పరిమాణంపై మెరుగైన ప్రభావాన్ని ఉత్పత్తి చేస్తుందని పై పరిస్థితి చూపిస్తుంది.జి.ఎస్= 0 వి.

అందుకే కాలువ లేదా బదిలీ లక్షణాలపై సానుకూల గేట్ వోల్టేజ్ ప్రాంతాన్ని సాధారణంగా పిలుస్తారు విస్తరణ ప్రాంతం . ఈ ప్రాంతం కట్-ఆఫ్ మరియు I యొక్క సంతృప్త స్థాయి మధ్య ఉందిడిఎస్ఎస్లేదా క్షీణత ప్రాంతం.

ఉదాహరణ సమస్యను పరిష్కరించడం

ప్రయోజనాలు మరియు అనువర్తనాలు

మెరుగుదల-మోడ్ MOSFET లకు విరుద్ధంగా, సున్నా గేట్-టు-సోర్స్ వోల్టేజ్కు ప్రతిస్పందనగా డ్రెయిన్ కరెంట్ సున్నాకి పడిపోవడాన్ని మేము కనుగొన్నాము, ఆధునిక క్షీణత-మోడ్ FET సున్నా గేట్ వోల్టేజ్తో గుర్తించదగిన విద్యుత్తును కలిగి ఉంది. ఖచ్చితంగా చెప్పాలంటే, డ్రెయిన్-టు-సోర్స్ నిరోధకత సాధారణంగా సున్నా వోల్టేజ్లో 100 ఓంలు.

పై గ్రాఫ్లో సూచించినట్లుగా, ON- రెసిస్టెన్స్ rds(పై)vs అనలాగ్ సిగ్నల్ పరిధి ఆచరణాత్మకంగా ఫ్లాట్ స్పందన వలె కనిపిస్తుంది. ఈ లక్షణం, ఈ అధునాతన క్షీణత రకం పరికరం యొక్క తక్కువ-కెపాసిటెన్స్ స్థాయిలతో కలిపి, ఆడియో మరియు వీడియో మార్పిడి అనువర్తనాల కోసం అనలాగ్ స్విచ్లు కావడంతో వాటిని ప్రత్యేకంగా అనువైనదిగా అనుమతిస్తుంది.

క్షీణత-మోడ్ MOSFET యొక్క 'సాధారణంగా-ఆన్' లక్షణం పరికరం సింగిల్ FET ప్రస్తుత నియంత్రకాలకు ఖచ్చితంగా సరిపోయేలా చేస్తుంది.

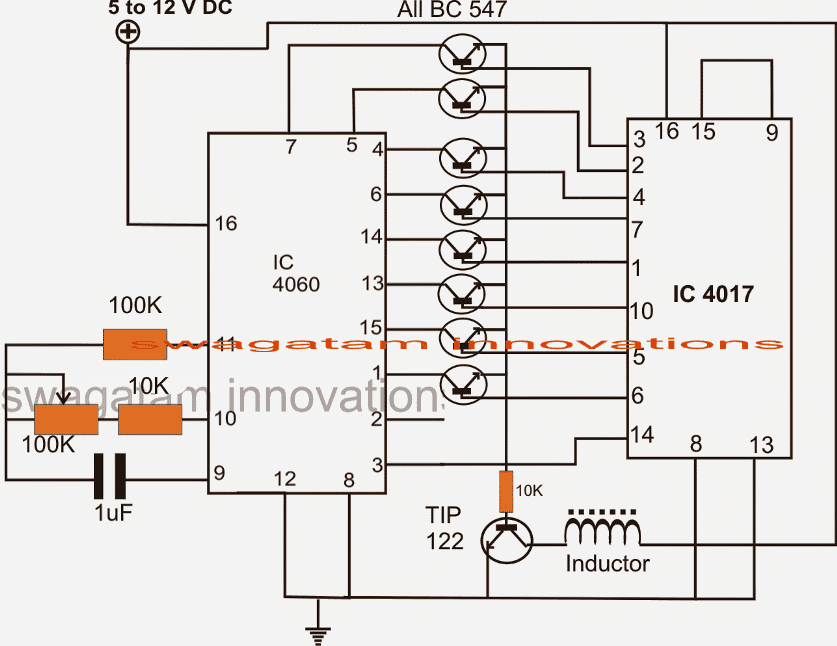

అటువంటి ఉదాహరణ సర్క్యూట్ కింది చిత్రంలో చూడవచ్చు.

సూత్రాన్ని ఉపయోగించి రూ. విలువను నిర్ణయించవచ్చు:

ఆర్s= VGSఆఫ్[1 - (నేనుడి/ నేనుడిఎస్ఎస్)1/2] / నేనుడి

ఎక్కడ నేనుడి అవుట్పుట్ వద్ద అవసరమైన నియంత్రిత కరెంట్ మొత్తం.

ప్రస్తుత-మూల అనువర్తనంలో క్షీణత-మోడ్ MOSFET ల యొక్క ప్రధాన ప్రయోజనం వాటి కనిష్ట కాలువ కెపాసిటెన్స్, ఇది తక్కువ-ఇన్పుట్ లీకేజ్, మీడియం-స్పీడ్ (> 50 V / us) సర్క్యూట్లలో అనువర్తనాలను పక్షపాతం చేయడానికి తగినదిగా చేస్తుంది.

దిగువ ఉన్న బొమ్మ డబుల్ తక్కువ-లీకేజ్ ఫంక్షన్ FET ను ఉపయోగించి తక్కువ-ఇన్పుట్-లీకేజ్ కరెంట్ డిఫరెన్షియల్ ఫ్రంట్-ఎండ్ను ప్రదర్శిస్తుంది.

సాధారణంగా, JFET యొక్క ఇరువైపులా ID = 500 uA వద్ద పక్షపాతం చూపబడుతుంది. అందువల్ల, పరిహారం మరియు విచ్చలవిడి కెపాసిటెన్స్లను వసూలు చేయడానికి ప్రస్తుతము పొందగలిగేది 2ID కి పరిమితం అవుతుంది లేదా ఇలాంటి సందర్భాల్లో 1.0 mA. JFET యొక్క సంబంధిత లక్షణాలు ఉత్పత్తి-నిరూపితమైనవి మరియు డేటాషీట్లో హామీ ఇవ్వబడతాయి.

Cs ఇన్పుట్ దశ 'తోక' ప్రస్తుత మూలం యొక్క అవుట్పుట్ కెపాసిటెన్స్ను సూచిస్తుంది. ఇన్పుట్ దశ ఈ నెట్వర్క్ అంతటా గణనీయమైన సిగ్నల్ ఎక్స్ఛేంజీలను అనుభవిస్తుంది మరియు C లలో ఛార్జింగ్ ప్రవాహాలు పెద్దవి కావడం వలన, ఇన్వర్టింగ్ కాని యాంప్లిఫైయర్లలో ఈ కెపాసిటెన్స్ చాలా ముఖ్యమైనది. సాధారణ ప్రస్తుత వనరులు ఉపయోగించినట్లయితే, ఇన్వర్టింగ్ కాని సర్క్యూట్లలో గుర్తించదగిన స్లీవ్-రేట్ క్షీణతకు ఈ తోక కెపాసిటెన్స్ జవాబుదారీగా ఉంటుంది (విలోమ అనువర్తనాలతో పోలిస్తే, ఇక్కడ C లలో ఛార్జింగ్ ప్రవాహాలు తక్కువగా ఉంటాయి).

వధించిన రేటులో తగ్గుదల ఇలా వ్యక్తీకరించబడుతుంది:

1/1+ (Cs / Sc)

Cs Cc (పరిహార కెపాసిటర్) కంటే తక్కువగా ఉన్నంతవరకు, వధించిన రేటులో ఎటువంటి వ్యత్యాసం ఉండదు. DMOS FET తో పనిచేయడం, C లు సుమారు 2 pF వరకు ఉంటాయి. ఈ వ్యూహం వధించిన రేటులో భారీ మెరుగుదలనిస్తుంది. 1 నుండి 5 mA కన్నా ఎక్కువ ప్రస్తుత లోటులు అవసరమైతే, పరికరం +2.5 V యొక్క గరిష్ట VGS కోసం 20 mA వరకు ఉత్పత్తి చేయడానికి మెరుగుదల మోడ్లో పక్షపాతం చూపవచ్చు, కనిష్ట అవుట్పుట్ కెపాసిటెన్స్ ఒక ముఖ్యమైన అంశంగా కొనసాగుతుంది.

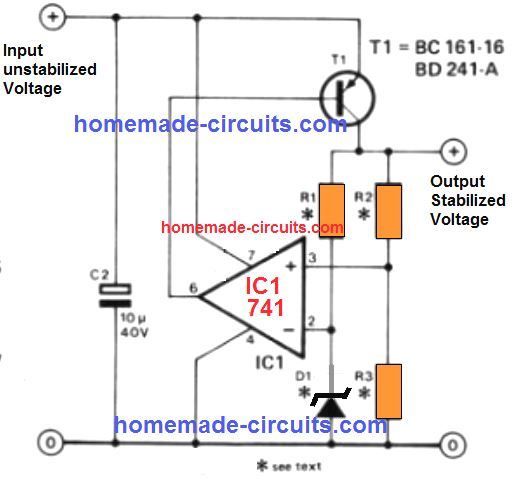

దిగువ తదుపరి అనువర్తనం సరైన మెరుగుదల-మోడ్ ప్రస్తుత సోర్స్ సర్క్యూట్ను ప్రదర్శిస్తుంది.

సరఫరా వోల్టేజ్ వైఫల్యం సమయంలో ప్రామాణిక పరిస్థితి అవసరమయ్యే అవసరాల కోసం 'సాధారణంగా -ఒక' అనలాగ్ స్విచ్ నిర్మించబడవచ్చు, ఉదాహరణకు పరీక్షా సాధనాల స్వయంచాలక శ్రేణిలో లేదా స్విచ్ ఆన్ వద్ద లాజిక్ సర్క్యూట్ల యొక్క ఖచ్చితమైన ప్రారంభాన్ని నిర్ధారించడానికి.

పరికరం యొక్క తగ్గిన నెగటివ్ థ్రెషోల్డ్ వోల్టేజ్ ప్రాథమిక డ్రైవ్ అవసరాలను అందిస్తుంది మరియు కనిష్ట వోల్టేజ్తో పనిచేయడానికి అనుమతిస్తుంది.

దిగువ సర్క్యూట్ ఏదైనా క్షీణత-మోడ్ DMOS అనలాగ్ స్విచ్ కోసం సాధారణ పక్షపాత కారకాలను ప్రదర్శిస్తుంది.

పరికరం స్విచ్ ఆఫ్ కావడానికి, గేట్ మీద ప్రతికూల వోల్టేజీలు అవసరం అవుతాయి. సానుకూల గేట్ వోల్టేజ్ను ఉపయోగించి FET అదనంగా మెరుగుపరచబడినప్పుడు ఆన్-రెసిస్టెన్స్ను తగ్గించవచ్చు, ఇది ప్రత్యేకంగా క్షీణత-మోడ్ ప్రాంతంతో పాటు మెరుగుదల-మోడ్ ప్రాంతంలో అనుమతిస్తుంది.

ఈ ప్రతిస్పందన క్రింది గ్రాఫ్లో చూడవచ్చు.

యూనిట్ యొక్క అధిక-ఫ్రీక్వెన్సీ లాభం, దాని తక్కువ కెపాసిటెన్స్ విలువలతో కలిపి, పెరిగిన 'ఫిగర్ ఆఫ్ మెరిట్' ను అందిస్తుంది. ఇది నిజంగా VHF మరియు UHF యాంప్లిఫికేషన్లో కీలకమైన అంశం, ఇది FET యొక్క లాభం-బ్యాండ్విడ్త్ ఉత్పత్తిని (GBW) నిర్దేశిస్తుంది, దీనిని ఇలా వర్ణించవచ్చు:

GBW = gfs / 2 పై (సిలో+ సిఅవుట్)

p- ఛానల్ క్షీణత-రకం MOSFET

పి-ఛానల్ క్షీణత-రకం మోస్ఫెట్ నిర్మాణం Fig.5.23 లో చూపిన n- ఛానల్ వెర్షన్ యొక్క ఖచ్చితమైన రివర్స్. అర్థం, ఉపరితలం ఇప్పుడు n- రకం రూపాన్ని తీసుకుంటుంది మరియు ఛానెల్ p- రకంగా మారుతుంది, క్రింద Fig.5.28a లో చూడవచ్చు.

టెర్మినల్ గుర్తింపు మారదు, కానీ వోల్టేజ్ మరియు ప్రస్తుత ధ్రువణతలు తారుమారు చేయబడతాయి, అదే చిత్రంలో సూచించినట్లు. కాలువ లక్షణాలు V తప్ప, Fig.5.25 లో వర్ణించబడ్డాయిడి.ఎస్ఈ సందర్భంలో ప్రతికూల విలువను పొందే గుర్తు.

కాలువ ప్రస్తుత I.డిఈ సందర్భంలో కూడా సానుకూల ధ్రువణతను చూపిస్తుంది, ఎందుకంటే మేము ఇప్పటికే దాని దిశను తిప్పికొట్టాము. విజి.ఎస్Fig.5.28c లో సూచించినట్లుగా, వ్యతిరేక ధ్రువణతను చూపిస్తుంది.

ఎందుకంటే విజి.ఎస్రివర్స్డ్ Fig.5,28b లో సూచించిన విధంగా బదిలీ లక్షణాల కోసం అద్దం చిత్రాన్ని ఉత్పత్తి చేస్తుంది.

అర్థం, సానుకూల V లో కాలువ ప్రవాహం పెరుగుతుందిజి.ఎస్V వద్ద కట్-ఆఫ్ పాయింట్ నుండి ప్రాంతంజి.ఎస్= నేను వరకు Vpడిఎస్ఎస్, అది V యొక్క ప్రతికూల విలువగా పెరుగుతూనే ఉంటుందిజి.ఎస్పెరుగుతుంది.

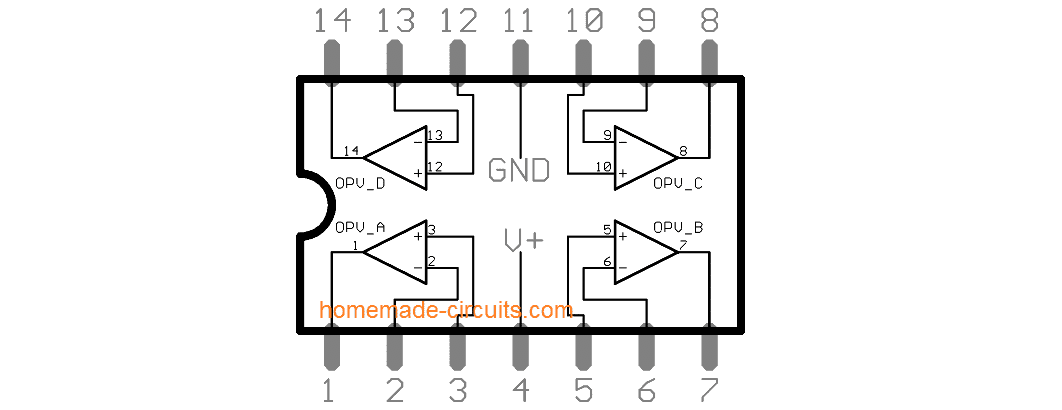

చిహ్నాలు

N- మరియు p- ఛానల్ క్షీణత-రకం MOSFET కోసం గ్రాఫికల్ సంకేతాలు పై అంజీర్ 5.29 లో చూడవచ్చు.

ఎంచుకున్న చిహ్నాలు పరికరం యొక్క నిజమైన నిర్మాణాన్ని సూచించే లక్ష్యాన్ని గమనించండి.

గేట్ మరియు ఛానల్ మధ్య ప్రత్యక్ష ఇంటర్ కనెక్షన్ లేకపోవడం (గేట్ ఇన్సులేషన్ కారణంగా) గేట్ మరియు చిహ్నం యొక్క విభిన్న టెర్మినల్స్ మధ్య అంతరం సూచిస్తుంది.

ఛానెల్ను సూచించే నిలువు వరుస కాలువ మరియు మూలం మధ్య జతచేయబడి, ఉపరితలం ద్వారా “పట్టుకొని” ఉంటుంది.

కొన్ని రకాల పరికరాలలో ఉపరితలం బాహ్యంగా ప్రాప్యత చేయవచ్చనే వాస్తవాన్ని హైలైట్ చేయడానికి ప్రతి రకం ఛానెల్ కోసం రెండు సమూహాల చిహ్నాలు పైన ఉన్న చిత్రంలో అమర్చబడి ఉంటాయి, మరికొన్నింటిలో ఇది కనిపించకపోవచ్చు.

MOSFET (వృద్ధి-రకం)

క్షీణత రకం మరియు మెరుగుదల రకం MOSFET లు వాటి అంతర్గత నిర్మాణాలు మరియు ఫంక్షనల్ మోడ్తో సమానంగా కనిపిస్తున్నప్పటికీ, వాటి లక్షణాలు చాలా భిన్నంగా ఉండవచ్చు.

కట్ ఆఫ్ చర్య కోసం గేట్-టు-సోర్స్ వోల్టేజ్ యొక్క నిర్దిష్ట స్థాయిపై ఆధారపడి ఉండే కాలువ ప్రవాహం ప్రధాన వ్యత్యాసం.

ఖచ్చితంగా, n- ఛానల్ మెరుగుదల-రకం MOSFET సానుకూల గేట్ / సోర్స్ వోల్టేజ్తో పనిచేయగలదు, బదులుగా ప్రతికూల సంభావ్యతల శ్రేణికి బదులుగా ఇది సాధారణంగా క్షీణత రకం MOSFET ను ప్రభావితం చేస్తుంది.

ప్రాథమిక నిర్మాణం

మీరు కింది వాటిలో n- ఛానల్ మెరుగుదల-రకం MOSFET ని దృశ్యమానం చేయవచ్చు

అంజీర్ 5.31.

పి-టైప్ మెటీరియల్ విభాగం సిలికాన్ బేస్ ద్వారా సృష్టించబడుతుంది మరియు దానిని నేర్చుకున్నట్లుగా దీనిని సబ్స్ట్రేట్ అని పిలుస్తారు.

కొన్ని సందర్భాల్లో ఈ ఉపరితలం క్షీణత-రకం MOSFET లో సోర్స్ పిన్తో అంతర్గతంగా జతచేయబడుతుంది, కొన్ని సందర్భాల్లో ఇది దాని సంభావ్య స్థాయి యొక్క బాహ్య నియంత్రణను ప్రారంభించడానికి నాల్గవ సీసంగా ముగించబడుతుంది.

మూలం మరియు కాలువ టెర్మినల్స్ ఎప్పటిలాగే n- డోప్డ్ ప్రాంతాలకు లోహ పరిచయాలను ఉపయోగించి చేరతాయి.

ఏదేమైనా, అంజీర్ 5.31 లో రెండు ఎన్-డోప్డ్ ప్రాంతాల మధ్య ఛానెల్ లేదు అని visual హించుకోవడం చాలా ముఖ్యం.

ఇది క్షీణత-రకం మరియు మెరుగుదల-రకం MOSFET యొక్క అంతర్గత లేఅవుట్ మధ్య ప్రాథమిక అసమానతగా పరిగణించబడుతుంది, ఇది పరికరంలో ఒక భాగమని భావించే స్వాభావిక ఛానెల్ లేకపోవడం.

SiO2 పొర ఇప్పటికీ ప్రబలంగా ఉంది, ఇది గేట్ టెర్మినల్ యొక్క లోహ బేస్ మరియు కాలువ మరియు మూలం మధ్య ఉన్న ప్రాంతం మధ్య ఒంటరిగా ఉండేలా చేస్తుంది. అయితే, ఇక్కడ ఇది పి-టైప్ మెటీరియల్ విభాగం నుండి వేరు చేయబడినట్లు చూడవచ్చు.

పై చర్చ నుండి, క్షీణత మరియు మెరుగుదల MOSFET అంతర్గత లేఅవుట్ కొన్ని సారూప్యతలను కలిగి ఉండవచ్చని మేము నిర్ధారించగలము, విస్తరణ రకం MOSFET కోసం కాలువ / మూలం మధ్య తప్పిపోయిన ఛానెల్ తప్ప.

ప్రాథమిక ఆపరేషన్ మరియు లక్షణాలు

దాని VGS వద్ద 0 V ప్రవేశపెట్టినప్పుడు విస్తరణ రకం MOSFET కోసం, తప్పిపోయిన n- ఛానల్ కారణంగా (ఇది చాలా ఉచిత క్యారియర్లను తీసుకువెళుతుంది) ప్రస్తుత ఉత్పత్తి సున్నాకి కారణమవుతుంది, ఇది క్షీణత రకానికి భిన్నంగా ఉంటుంది ID = IDSS కలిగి ఉన్న MOSFET యొక్క.

డ్రెయిన్ / సోర్స్ టెర్మినల్స్ అంతటా తప్పిపోయిన మార్గం కారణంగా అటువంటి పరిస్థితిలో, ఎలక్ట్రాన్ల రూపంలో పెద్ద మొత్తంలో క్యారియర్లు కాలువ / మూలం వద్ద పేరుకుపోలేవు (ఎందుకంటే ఎన్-డోప్డ్ ప్రాంతాలు).

VDS వద్ద కొంత సానుకూల సామర్థ్యాన్ని వర్తింపజేయడం, VGS సున్నా వోల్ట్ల వద్ద సెట్ చేయబడి, SS టెర్మినల్ సోర్స్ టెర్మినల్తో చిన్నదిగా ఉండటంతో, వాస్తవానికి n- డోప్డ్ ప్రాంతాలు మరియు p- సబ్స్ట్రేట్ మధ్య రివర్స్ బయాస్డ్ pn జంక్షన్లను కనుగొంటాము. మూలానికి ప్రవహిస్తుంది.

అంజీర్ 5.32 లో VDS మరియు VGS 0 V కన్నా ఎక్కువ సానుకూల వోల్టేజ్తో వర్తించే పరిస్థితిని చూపిస్తుంది, ఇది కాలువ మరియు గేట్ మూలానికి సంబంధించి సానుకూల సామర్థ్యంతో ఉండటానికి అనుమతిస్తుంది.

గేట్ వద్ద ఉన్న సానుకూల సంభావ్యత, పై చిత్రంలో చూపిన విధంగా, పి-సబ్స్ట్రేట్లోని రంధ్రాలను SiO2 పొర యొక్క అంచున ఉన్న ప్రదేశానికి బయలుదేరి, పి-సబ్స్ట్రేట్ యొక్క ప్రాంతాలలోకి లోతుగా ప్రవేశిస్తుంది. ఒకరినొకరు తిప్పికొట్టే ఇలాంటి ఆరోపణల వల్ల ఇది జరుగుతుంది.

ఇది రంధ్రాలు లేని శూన్యమైన SiO2 ఇన్సులేటింగ్ పొరకు దగ్గరగా క్షీణత ప్రాంతం సృష్టించబడుతుంది.

అయినప్పటికీ, పదార్థం యొక్క మైనారిటీ క్యారియర్లైన పి-సబ్స్ట్రేట్ ఎలక్ట్రాన్లు సానుకూల ద్వారం వైపుకు లాగి, SiO2 పొర యొక్క ఉపరితలానికి దగ్గరగా ఉన్న ప్రాంతంలో సేకరించడం ప్రారంభిస్తాయి.

SiO2 లేయర్ యొక్క ఇన్సులేషన్ ఆస్తి కారణంగా ప్రతికూల క్యారియర్లు గేట్ టెర్మినల్ వద్ద ప్రతికూల క్యారియర్లను గ్రహించకుండా అనుమతిస్తాయి.

మేము VGS స్థాయిని పెంచుతున్నప్పుడు, SiO2 ఉపరితలానికి దగ్గరగా ఉన్న ఎలక్ట్రాన్ సాంద్రత కూడా పెరుగుతుంది, చివరకు ప్రేరిత n- రకం ప్రాంతం కాలువ / మూలం అంతటా లెక్కించదగిన ప్రసరణను అనుమతించగలదు.

కాలువ ప్రవాహంలో సరైన పెరుగుదలకు కారణమయ్యే VGS మాగ్నిట్యూడ్ను థ్రెషోల్డ్ వోల్టేజ్ అంటారు, VT చిహ్నం ద్వారా సూచించబడుతుంది . డేటాషీట్లలో మీరు దీనిని VGS (Th) గా చూడగలరు.

పైన నేర్చుకున్నట్లుగా, VGS = 0 వద్ద ఛానెల్ లేకపోవడం మరియు సానుకూల గేట్-టు-సోర్స్ వోల్టేజ్ అనువర్తనంతో 'మెరుగుపరచబడినది' కారణంగా, ఈ రకమైన MOSFET ను మెరుగుదల-రకం MOSFET లు అంటారు.

క్షీణత- మరియు మెరుగుదల-రకం MOSFET లు మెరుగుదల-రకం ప్రాంతాలను ప్రదర్శిస్తాయని మీరు కనుగొంటారు, కానీ ఈ పదం మెరుగుదల తరువాతి కోసం ఉపయోగించబడుతుంది ఎందుకంటే ఇది ఆపరేషన్ యొక్క మెరుగుదల మోడ్ను ఉపయోగించి ప్రత్యేకంగా పనిచేస్తుంది.

ఇప్పుడు, VGS ప్రవేశ విలువపైకి నెట్టివేయబడినప్పుడు, ఉచిత క్యారియర్ల ఏకాగ్రత అది ప్రేరేపించబడిన ఛానెల్లో పెరుగుతుంది. దీనివల్ల కాలువ ప్రవాహం పెరుగుతుంది.

మరోవైపు, మేము VGS ని స్థిరంగా ఉంచి, VDS (డ్రెయిన్-టు-సోర్స్ వోల్టేజ్) స్థాయిని పెంచుకుంటే, ఇది చివరికి MOSFET దాని సంతృప్త స్థానానికి చేరుకుంటుంది, సాధారణంగా ఏదైనా JFET లేదా క్షీణత MOSFET కు కూడా ఇది జరుగుతుంది.

అంజీర్ 5.33 లో చూపినట్లుగా, కాలువ కరెంట్ ఐడి పిన్చింగ్-ఆఫ్ ప్రాసెస్ సహాయంతో సమం అవుతుంది, ఇది ప్రేరేపిత ఛానెల్ యొక్క కాలువ చివర వైపు ఇరుకైన ఛానెల్ ద్వారా సూచించబడుతుంది.

అంజీర్ 5.33 లోని మోస్ఫెట్ యొక్క టెర్మినల్ వోల్టేజ్లకు కిర్చాఫ్ యొక్క వోల్టేజ్ చట్టాన్ని వర్తింపజేయడం ద్వారా, మనకు లభిస్తుంది:

VGS ని ఒక నిర్దిష్ట విలువకు స్థిరంగా ఉంచినట్లయితే, ఉదాహరణకు 8 V, మరియు VDS ను 2 నుండి 5 V కి పెంచారు, వోల్టేజ్ VDG ద్వారా Eq. 5.11 -6 నుండి -3 V కి పడిపోవడాన్ని చూడవచ్చు మరియు కాలువ వోల్టేజీకి సంబంధించి గేట్ సంభావ్యత తక్కువ మరియు తక్కువ సానుకూలతను పొందుతుంది.

ఈ ప్రతిస్పందన ఉచిత క్యారియర్లు లేదా ఎలక్ట్రాన్లు ప్రేరేపిత ఛానెల్ యొక్క ఈ ప్రాంతం వైపుకు లాగకుండా నిషేధిస్తుంది, దీని ఫలితంగా ఛానెల్ యొక్క ప్రభావవంతమైన వెడల్పు తగ్గుతుంది.

అంతిమంగా, ఛానెల్ వెడల్పు చిటికెడు-ఆఫ్ స్థాయికి తగ్గుతుంది, ఇది మన మునుపటి క్షీణత MOSFET కథనంలో ఇప్పటికే నేర్చుకున్న మాదిరిగానే సంతృప్త స్థితికి చేరుకుంటుంది.

అర్థం, స్థిరమైన VGS తో VDS ని పెంచడం ID యొక్క సంతృప్త స్థాయిని ప్రభావితం చేయదు, విచ్ఛిన్న పరిస్థితి వచ్చే వరకు.

అంజీర్ 5.34 ను చూస్తే, VGS = 8 V కలిగి ఉన్న Fig.5.33 లో ఉన్నట్లుగా, MOSFET కొరకు, సంతృప్తత 6 V యొక్క VDS స్థాయిలో జరుగుతుంది. ఖచ్చితంగా చెప్పాలంటే VDS సంతృప్త స్థాయి అనువర్తిత VGS స్థాయికి అనుబంధించబడుతుంది:

నిస్సందేహంగా, VT విలువ స్థిరంగా ఉన్నప్పుడు, VGS స్థాయిని పెంచడం అనులోమానుపాతంలో సంతృప్త స్థాయిల యొక్క లోకస్ ద్వారా VDS కొరకు అధిక స్థాయి సంతృప్తిని కలిగిస్తుంది.

పై చిత్రంలో చూపిన లక్షణాలను సూచిస్తూ, VT స్థాయి 2 V, ఇది కాలువ ప్రవాహం 0 mA కి పడిపోయిందని స్పష్టంగా తెలుస్తుంది.

అందువల్ల సాధారణంగా మనం ఇలా చెప్పగలం:

వృద్ధి-రకం MOSFET కోసం VGS విలువలు ప్రవేశ స్థాయి కంటే తక్కువగా ఉన్నప్పుడు, దాని కాలువ ప్రవాహం 0 mA.

VGS ను VT నుండి 8 V కి పెంచినంతవరకు, ID కోసం సంబంధిత సంతృప్త స్థాయి కూడా 0 నుండి 10 mA స్థాయికి పెరుగుతుందని పై చిత్రంలో మనం స్పష్టంగా చూడవచ్చు.

అంతేకాకుండా, VGS విలువల పెరుగుదలతో VGS స్థాయిల మధ్య స్థలం పెరుగుతుందని, కాలువ ప్రవాహంలో అనంతమైన పెరుగుదలకు కారణమవుతుందని మనం గమనించవచ్చు.

కాలువ ప్రస్తుత విలువ VT కన్నా ఎక్కువ VGS స్థాయిల కోసం గేట్-టు-సోర్స్ వోల్టేజ్కు సంబంధించినది, ఈ క్రింది నాన్ లీనియర్ రిలేషన్ ద్వారా:

స్క్వేర్డ్ బ్రాకెట్ చూపబడిన పదం ఐడి మరియు విజిఎస్ మధ్య నాన్ లీనియర్ రిలేటిన్షిప్కు బాధ్యత వహిస్తుంది.

K అనే పదం స్థిరంగా ఉంటుంది మరియు ఇది MOSFET లేఅవుట్ యొక్క పని.

కింది సమీకరణం ద్వారా ఈ స్థిరమైన k యొక్క విలువను మనం తెలుసుకోవచ్చు:

ఇక్కడ ID (ఆన్) మరియు VGD (ఆన్) ప్రతి ఒక్కటి ప్రత్యేకంగా పరికరం యొక్క లక్షణాన్ని బట్టి విలువలు.

దిగువ ఉన్న అంజీర్ 5.35 లో, బదిలీ ప్రక్రియను ఒకదానికొకటి స్పష్టం చేయడానికి కాలువ మరియు బదిలీ లక్షణాలు ఒకదానికొకటి అమర్చబడి ఉన్నాయని మేము కనుగొన్నాము.

సాధారణంగా, ఇది JFET మరియు క్షీణత-రకం MOSFET ల కోసం గతంలో వివరించిన ప్రక్రియకు సమానంగా ఉంటుంది.

అయితే, ప్రస్తుత సందర్భంలో, VGS VT కి డ్రెయిన్ కరెంట్ 0 mA అని గుర్తుంచుకోవాలి.

ఇక్కడ ID గమనించదగ్గ కరెంట్ను చూడవచ్చు, ఇది Eq ద్వారా నిర్ణయించబడుతుంది. 5.13.

గమనిక, కాలువ లక్షణాల నుండి బదిలీ లక్షణాలపై పాయింట్లను నిర్వచించేటప్పుడు, మేము సంతృప్త స్థాయిలను మాత్రమే పరిశీలిస్తాము. ఇది ఆపరేషన్ ప్రాంతాన్ని EQ చేత స్థాపించబడిన సంతృప్త స్థాయిల కంటే ఎక్కువ VDS విలువలకు పరిమితం చేస్తుంది. (5.12).

p- ఛానల్ వృద్ధి-రకం MOSFET లు

అంజీర్ 5.37a లో చూపిన విధంగా p- ఛానల్ మెరుగుదల-రకం MOSFET యొక్క నిర్మాణం అంజీర్ 5.31 లో చూపిన దానికి వ్యతిరేకం.

అర్థం, ఇప్పుడు మీరు కాలువ మరియు మూల కీళ్ల క్రింద n- రకం ఉపరితలం మరియు పి-డోప్డ్ ప్రాంతాలు ఉన్నట్లు కనుగొన్నారు.

టెర్మినల్స్ స్థాపించబడినట్లుగా కొనసాగుతున్నాయి, కానీ ప్రస్తుత ప్రతి దిశలు మరియు వోల్టేజ్ ధ్రువణతలు తారుమారు చేయబడతాయి.

కాలువ లక్షణాలు అంజీర్ 5.37 సిలో ఇచ్చినట్లుగా కనిపిస్తాయి, VGS యొక్క నిరంతర ప్రతికూల మాగ్నిట్యూడ్ల వల్ల పెరుగుతున్న కరెంట్ మొత్తాన్ని కలిగి ఉంటుంది.

బదిలీ లక్షణాలు అంజీర్ 5.35 యొక్క బదిలీ వక్రత యొక్క అద్దం ముద్ర (ID అక్షం చుట్టూ), Fig. 5.37b లో చూపిన విధంగా VT పైన VGS యొక్క మరింత ప్రతికూల విలువలతో ID పెరుగుతుంది. (5.14) ద్వారా (5.14) సమీకరణాలు పి-ఛానల్ పరికరాలకు కూడా తగినవి.

ప్రస్తావనలు:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

మునుపటి: యాంటీ స్పై RF డిటెక్టర్ సర్క్యూట్ - వైర్లెస్ బగ్ డిటెక్టర్ తర్వాత: బదిలీ లక్షణాలు