RISC V అనేది యూనివర్శిటీ ఆఫ్ కాలిఫోర్నియా, బర్కిలీచే అభివృద్ధి చేయబడిన ఒక ఇన్స్ట్రక్షన్ సెట్ ఆర్కిటెక్చర్. RISC యొక్క భావన చాలా వరకు ప్రాసెసర్ సూచనలను చాలా కంప్యూటర్ ప్రోగ్రామ్లు ఉపయోగించలేదనే నిజం ద్వారా ప్రేరేపించబడింది. కాబట్టి, డిజైన్లలో అనవసరమైన డీకోడింగ్ లాజిక్ ఉపయోగించబడుతోంది ప్రాసెసర్లు , మరింత శక్తి అలాగే ప్రాంతం వినియోగిస్తుంది. సూచనల సమితిని తగ్గించడానికి & రిజిస్టర్ వనరులలో ఎక్కువ పెట్టుబడి పెట్టడానికి, ది RISC V ప్రాసెసర్ అమలు చేయబడింది.

ఈ సాంకేతికతను చాలా మంది టెక్ దిగ్గజాలు మరియు స్టార్ట్-అప్లు గమనించారు ఎందుకంటే ఇది పూర్తిగా ఓపెన్ సోర్స్ & ఉచితం. చాలా రకాల ప్రాసెసర్లు లైసెన్స్ ఒప్పందంతో అందుబాటులో ఉన్నాయి, అయితే ఈ రకమైన ప్రాసెసర్తో; ఎవరైనా తమ కొత్త ప్రాసెసర్ డిజైన్లను తయారు చేసుకోవచ్చు. కాబట్టి ఈ కథనం RISC V ప్రాసెసర్ - పని మరియు దాని అప్లికేషన్ల యొక్క అవలోకనాన్ని చర్చిస్తుంది.

RISC V ప్రాసెసర్ అంటే ఏమిటి?

RISC V ప్రాసెసర్లో, RISC అనే పదం 'తగ్గిన ఇన్స్ట్రక్షన్ సెట్ కంప్యూటర్' అని సూచిస్తుంది, ఇది కొన్ని కంప్యూటర్ సూచనలను అమలు చేస్తుంది, అయితే 'V' అనేది 5వ తరం. ఇది స్థాపించబడిన సూత్రం ఆధారంగా ఓపెన్ సోర్స్ హార్డ్వేర్ ISA (ఇన్స్ట్రక్షన్ సెట్ ఆర్కిటెక్చర్). ప్రమాదం .

ఇతర ISA డిజైన్లతో పోలిస్తే, ఈ ISA ఓపెన్ సోర్స్ లైసెన్స్తో అందుబాటులో ఉంది. కాబట్టి, అనేక తయారీ కంపెనీలు ఓపెన్ సోర్స్ ఆపరేటింగ్ సిస్టమ్లతో RISC-V హార్డ్వేర్ను ప్రకటించాయి మరియు అందించాయి.

ఇది కొత్త ఆర్కిటెక్చర్ మరియు ఓపెన్, నాన్-రిస్ట్రిక్టివ్ & ఉచిత లైసెన్స్లలో అందుబాటులో ఉంది. ఈ ప్రాసెసర్కు చిప్ & డివైజ్ మేకర్స్ పరిశ్రమల నుండి విస్తృతమైన మద్దతు ఉంది. కనుక ఇది ప్రధానంగా అనేక అప్లికేషన్లలో ఉపయోగించడానికి ఉచితంగా విస్తరించదగిన & అనుకూలీకరించదగినదిగా రూపొందించబడింది.

RISC V చరిత్ర

RISCని 1980లో బర్కిలీలోని కాలిఫోర్నియా విశ్వవిద్యాలయంలో ప్రొఫెసర్. డేవిడ్ ప్యాటర్సన్ కనుగొన్నారు. ప్రొఫెసర్ డేవిడ్, ప్రొఫెసర్ జాన్ హెన్నెస్సీతో కలిసి “కంప్యూటర్ ఆర్గనైజేషన్ అండ్ డిజైన్” & “కంప్యూటర్ ఆర్కిటెక్చర్ ఎట్ స్టాన్ఫోర్డ్ యూనివర్శిటీ” అనే రెండు పుస్తకాలలో తమ ప్రయత్నాలను సమర్పించారు. కాబట్టి, వారు ACM A.M. 2017 సంవత్సరంలో ట్యూరింగ్ అవార్డు.

1980 నుండి 2010 సంవత్సరం వరకు, RISC ఐదవ తరం అభివృద్ధి పరిశోధన ప్రారంభించబడింది మరియు చివరకు RISC-Vగా గుర్తించబడింది, ఇది ప్రమాదం ఐదుగా ఉచ్ఛరిస్తారు.

RISC V ఆర్కిటెక్చర్ & వర్కింగ్

RV12 RISC V ఆర్కిటెక్చర్ క్రింద చూపబడింది. ఎంబెడెడ్ ఫీల్డ్లలో ఉపయోగించే సింగిల్-కోర్ RV32I మరియు RV64I కంప్లైంట్ RISC CPUతో RV12 అత్యంత కాన్ఫిగర్ చేయబడుతుంది. పారిశ్రామిక ప్రామాణిక RISC-V సూచనల సెట్పై ఆధారపడి RV12 కూడా 32 లేదా 64-బిట్ CPU కుటుంబం నుండి వచ్చింది.

RV12 కేవలం ఇన్స్ట్రక్షన్ మరియు డేటా మెమరీకి ఏకకాల యాక్సెస్ కోసం హార్వర్డ్ ఆర్కిటెక్చర్ను అమలు చేస్తుంది. ఇది 6-దశల పైప్లైన్ను కూడా కలిగి ఉంటుంది, ఇది ఎగ్జిక్యూషన్ మరియు మెమరీ యాక్సెస్ల మధ్య ఓవర్ల్యాప్లను ఆప్టిమైజ్ చేయడంలో సహాయపడుతుంది. ఈ నిర్మాణంలో ప్రధానంగా బ్రాంచ్ ప్రిడిక్షన్, డేటా కాష్, డీబగ్ యూనిట్, ఇన్స్ట్రక్షన్ కాష్ & ఐచ్ఛిక మల్టిప్లైయర్ లేదా డివైడర్ యూనిట్లు ఉంటాయి.

RV12 RISC V యొక్క ప్రధాన లక్షణాలు క్రింది వాటిని కలిగి ఉన్నాయి.

- ఇది ఇండస్ట్రీ స్టాండర్డ్ ఇన్స్ట్రక్షన్ సెట్.

- 32 లేదా 64బిట్ డేటాతో పారామీటర్ చేయబడింది.

- ఇది ఖచ్చితమైన మరియు వేగవంతమైన అంతరాయాలను కలిగి ఉంది.

- అనుకూల సూచనలు యాజమాన్య హార్డ్వేర్ యాక్సిలరేటర్లను జోడించడాన్ని అనుమతిస్తాయి.

- సింగిల్ సైకిల్ అమలు.

- ఆప్టిమైజింగ్ మడతతో ఆరు-దశల పైప్లైన్.

- మెమరీ రక్షణతో మద్దతు.

- ఐచ్ఛికం లేదా పారామీటర్ కాష్లు.

- అత్యంత పరామితి.

- వినియోగదారులు 32/ 64-బిట్ డేటా & బ్రాంచ్ ప్రిడిక్షన్ యూనిట్ని ఎంచుకోవచ్చు.

- వినియోగదారులు సూచన/డేటా కాష్లను ఎంచుకోవచ్చు.

- వినియోగదారు ఎంచుకోదగిన నిర్మాణం, పరిమాణం & కాష్ నిర్మాణం.

- వినియోగదారు నిర్వచించిన జాప్యం ద్వారా హార్డ్వేర్ డివైడర్ లేదా మల్టిప్లైయర్ సపోర్ట్.

- బస్సు నిర్మాణం అనువైనది, ఇది విష్బోన్ & AHBకి మద్దతు ఇస్తుంది.

- ఈ డిజైన్ శక్తి & పరిమాణాన్ని ఆప్టిమైజ్ చేస్తుంది.

- పనితీరు లేదా పవర్ ట్రేడ్ఆఫ్లను అందించే డిజైన్ పూర్తిగా పరామితి చేయబడింది.

- శక్తిని తగ్గించడానికి గేటెడ్ CLK డిజైన్.

- ఇండస్ట్రీ స్టాండర్డ్ ద్వారా సాఫ్ట్వేర్ మద్దతు.

- ఆర్కిటెక్చరల్ సిమ్యులేటర్.

- ఎక్లిప్స్ IDE Linux/ Windows కోసం ఉపయోగించబడుతుంది.

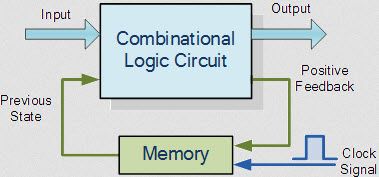

RISC V ఎగ్జిక్యూషన్ పైప్లైన్

ఇందులో IF (ఇన్స్ట్రక్షన్ ఫెచ్), ID (ఇన్స్ట్రక్షన్ డీకోడ్), EX (ఎగ్జిక్యూట్), MEM (మెమరీ యాక్సెస్) & WB (రిజిస్టర్ రైట్-బ్యాక్) వంటి ఐదు దశలు ఉన్నాయి.

సూచన పొందడం

ఇన్స్ట్రక్షన్ ఫెచ్ లేదా IF దశలో, ప్రోగ్రామ్ కౌంటర్ (PC) మరియు ఇన్స్ట్రక్షన్ మెమరీ నుండి ఒకే సూచన చదవబడుతుంది, ఇది తదుపరి సూచనకు నవీకరించబడుతుంది.

సూచన ప్రీ-డీకోడ్

RVC మద్దతు అనుమతించబడిన తర్వాత, ఇన్స్ట్రక్షన్ ప్రీ-డీకోడ్ దశ 16-బిట్-కంప్రెస్డ్ ఇన్స్ట్రక్షన్ను స్థానిక 32-బిట్ ఇన్స్ట్రక్షన్గా డీకోడ్ చేస్తుంది.

ఇన్స్ట్రక్షన్ డీకోడ్

ఇన్స్ట్రక్షన్ డీకోడ్ (ID) దశలో, రిజిస్టర్ ఫైల్ అనుమతించబడుతుంది & బైపాస్ నియంత్రణలు నిర్ణయించబడతాయి.

అమలు చేయండి

ఎగ్జిక్యూట్ దశలో, ఫలితం ALU, DIV, MUL సూచనల కోసం గణించబడుతుంది, స్టోర్ లేదా లోడ్ సూచనల కోసం అనుమతించబడిన మెమరీ, మరియు బ్రాంచ్లు & జంప్లు వాటి ఆశించిన ఫలితాలతో కొలవబడతాయి.

జ్ఞాపకశక్తి

ఈ మెమరీ దశలో, మెమరీ పైప్లైన్ ద్వారా యాక్సెస్ చేయబడుతుంది. ఈ దశను చేర్చడం పైప్లైన్ యొక్క అధిక పనితీరును నిర్ధారిస్తుంది.

తిరిగి వ్రాయు

ఈ దశలో, ఎగ్జిక్యూషన్ దశ ఫలితం రిజిస్టర్ ఫైల్లో వ్రాయబడుతుంది.

బ్రాంచ్ ప్రిడిక్టర్

ఈ ప్రాసెసర్లో బ్రాంచ్ ప్రిడిక్టర్ యూనిట్ లేదా BPU ఉంటుంది, ఇది నిర్దిష్ట బ్రాంచ్ని తీసుకోవాలా వద్దా అని నిర్ణయించడంలో RISC V ప్రాసెసర్కు మార్గనిర్దేశం చేయడానికి గత డేటాను నిల్వ చేయడానికి ఉపయోగించబడుతుంది. బ్రాంచ్ ఎగ్జిక్యూట్ అయిన తర్వాత ఈ ప్రిడిక్టర్ డేటా అప్డేట్ చేయబడుతుంది.

ఈ యూనిట్ దాని ప్రవర్తనను నిర్ణయించే విభిన్న పారామితులను కలిగి ఉంటుంది. ఉదాహరణకు, HAS_BPU అనేది యూనిట్ ఉనికిని అంచనా వేస్తుందో లేదో నిర్ణయించడానికి HAS_BPU ఉపయోగించబడుతుంది, BPU_GLOBAL_BITS ఎన్ని గత బిట్లను ఉపయోగించాలో నిర్ణయిస్తుంది మరియు ప్రోగ్రామ్ కౌంటర్ యొక్క LSBలో ఎన్ని ఉపయోగించాలో BPU_LOCAL_BITS నిర్ణయిస్తుంది. BPU_LOCAL_BITS & BPU_GLOBAL_BITS కలయిక బ్రాంచ్-ప్రిడిక్షన్-టేబుల్ను పరిష్కరించడానికి ప్రధానంగా ఉపయోగించబడే వెక్టర్ను సృష్టిస్తుంది.

డేటా కాష్

కొత్తగా యాక్సెస్ చేయబడిన మెమరీ స్థానాలను బఫర్ చేయడం ద్వారా డేటా మెమరీ యాక్సెస్ను వేగవంతం చేయడానికి ఇది ప్రధానంగా ఉపయోగించబడుతుంది. ఇది హాఫ్-వర్డ్, బైట్ & వర్డ్ యాక్సెస్లను XLEN = 32 వారి స్వంత సరిహద్దుల్లో ఉన్నట్లయితే వాటిని హ్యాండిల్ చేయగలదు. ఇది హాఫ్-వర్డ్, బైట్, వర్డ్ & డబుల్-వర్డ్ యాక్సెస్లను XLEN=64 వారి స్వంత సరిహద్దుల్లో ఉన్నట్లయితే వాటిని కూడా నిర్వహించగలదు.

కాష్ మిస్ మొత్తం, మొత్తం బ్లాక్ మెమరీకి తిరిగి వ్రాయబడుతుంది, కాబట్టి అవసరమైతే, కాష్లోకి కొత్త బ్లాక్ను లోడ్ చేయవచ్చు. DCACHE_SIZEని సున్నాకి సెట్ చేయడం ద్వారా డేటా కాష్ నిలిపివేయబడుతుంది. ఆ తర్వాత, మెమరీ స్థానాలు నేరుగా ద్వారా యాక్సెస్ చేయబడతాయి డేటా ఇంటర్ఫేస్ .

సూచన కాష్

ఇది ప్రధానంగా కొత్తగా పొందిన సూచనలను బఫర్ చేయడం ద్వారా సూచనలను పొందడాన్ని వేగవంతం చేయడానికి ఉపయోగించబడుతుంది. ఈ కాష్ ఏదైనా 16-బిట్ సరిహద్దులో ప్రతి సైకిల్కు ఒక పార్శిల్ను పొందేందుకు ఉపయోగించబడుతుంది కానీ బ్లాక్ సరిహద్దులో కాదు. కాష్ మిస్లో, ఇన్స్ట్రక్షన్ మెమరీ నుండి మొత్తం బ్లాక్ను లోడ్ చేయవచ్చు. ఈ కాష్ యొక్క కాన్ఫిగరేషన్ వినియోగదారు అవసరాల ఆధారంగా చేయవచ్చు. కాష్ పరిమాణం, రీప్లేస్మెంట్ అల్గోరిథం మరియు బ్లాక్ పొడవు కాన్ఫిగర్ చేయబడతాయి.

ICACHE_SIZEని సున్నాకి సెట్ చేయడం ద్వారా సూచన చక్రం నిలిపివేయబడుతుంది. ఆ తర్వాత, మెమరీ నుండి నేరుగా పార్సెల్లు పొందబడతాయి ఇన్స్ట్రక్షన్ ఇంటర్ఫేస్.

డీబగ్ యూనిట్

డీబగ్ యూనిట్ డీబగ్ పరిసరాలను ఆపడానికి మరియు CPUని పరిశీలించడానికి అనుమతిస్తుంది. బ్రాంచ్ ట్రేసింగ్, 8- హార్డ్వేర్ బ్రేక్పాయింట్ల వరకు సింగిల్ స్టెప్ ట్రేసింగ్ ఇందులోని ప్రధాన లక్షణాలు.

రిజిస్టర్ ఫైల్

ఇది X0 నుండి X31 వరకు 32 రిజిస్టర్ స్థానాలతో రూపొందించబడింది, ఇక్కడ X9 రిజిస్టర్ ఎల్లప్పుడూ సున్నాగా ఉంటుంది. రిజిస్టర్ ఫైల్లో 1- రైట్ పోర్ట్ & 2-రీడ్ పోర్ట్లు ఉన్నాయి.

కాన్ఫిగర్ చేయగల ఇంటర్ఫేస్

ఈ ప్రాసెసర్ వివిధ బాహ్య బస్సు ఇంటర్ఫేస్లకు మద్దతు ఇచ్చే బాహ్య ఇంటర్ఫేస్.

RISC V ఎలా పని చేస్తుంది?

RISC-V అనేది RISC (రిడ్యూస్డ్ ఇన్స్ట్రక్షన్ సెట్ కంప్యూటర్) సూత్రాలలో రూట్ చేయబడిన ఇన్స్ట్రక్షన్ సెట్ ఆర్కిటెక్చర్. ఈ ప్రాసెసర్ చాలా ప్రత్యేకమైనది మరియు విప్లవాత్మకమైనది, ఎందుకంటే ఇది ఉచిత, సాధారణ మరియు ఓపెన్-సోర్స్ ISA, ఇక్కడ హార్డ్వేర్ను అభివృద్ధి చేయవచ్చు, సాఫ్ట్వేర్ను పోర్ట్ చేయవచ్చు & ప్రాసెసర్లను సపోర్ట్ చేయడానికి డిజైన్ చేయవచ్చు.

తేడా B/W RISC V Vs MIPS

RISC V మరియు MIPS మధ్య వ్యత్యాసం క్రింది వాటిని కలిగి ఉంటుంది.

|

RISC వి |

MIPS |

| RISC V అనే పదం తగ్గిన ఇన్స్ట్రక్షన్ సెట్ కంప్యూటర్ని సూచిస్తుంది, ఇక్కడ 'V' ఐదవ తరం. | 'MIPS' అనే పదం 'సెకనుకు మిలియన్ సూచనలు' అని సూచిస్తుంది. |

| RISC-V కేవలం చిన్న పరికరాల తయారీదారులను చెల్లించకుండా హార్డ్వేర్ను రూపొందించడానికి అనుమతిస్తుంది. | MIPS తయారీదారుని చెల్లించడం ద్వారా ప్రాసెసర్ వేగాన్ని కొలవడానికి అనుమతిస్తుంది ఎందుకంటే ఇది ఉచితం కాదు. |

| MIPS సమర్థవంతంగా చనిపోయింది. | RISC-V సమర్థవంతంగా చనిపోలేదు. |

| ఈ ప్రాసెసర్ రెండు రిజిస్టర్లను పోల్చడానికి శాఖ సూచనలను అందిస్తుంది. | కాంట్రాస్ట్ నిజమా కాదా అనే దాని ఆధారంగా 1 లేదా 0కి రిజిస్టర్ను గుర్తించే పోలిక సూచనపై MIPS ఆధారపడి ఉంటుంది. |

| ISA ఎన్కోడింగ్ పథకం RISC Vలో స్థిరమైనది & వేరియబుల్. | ISA ఎన్కోడింగ్ పథకం MIPSలో పరిష్కరించబడింది |

| సూచనల సెట్ పరిమాణం 16-బిట్ లేదా 32-బిట్ లేదా 64-బిట్ లేదా 128-బిట్. | సూచనల సెట్ పరిమాణం 32-బిట్ లేదా 64-బిట్. |

| ఇది 32 సాధారణ ప్రయోజనం & ఫ్లోటింగ్ పాయింట్ రిజిస్టర్లను కలిగి ఉంది | ఇది 31 సాధారణ ప్రయోజనం & ఫ్లోటింగ్ పాయింట్ రిజిస్టర్లను కలిగి ఉంది. |

| ఇది 26-సింగిల్ & డబుల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. | ఇది 15-సింగిల్ & డబుల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. |

తేడా B/W RISC V Vs ARM

RISC V Vs ARM మధ్య వ్యత్యాసం క్రింది వాటిని కలిగి ఉంటుంది.

|

RISC వి |

ARM |

| RISC-V అనేది ఓపెన్ సోర్స్, కాబట్టి దీనికి ఎలాంటి లైసెన్స్ అవసరం లేదు. | ARM ఒక క్లోజ్డ్ సోర్స్, కాబట్టి దీనికి లైసెన్స్ అవసరం. |

| ఇది ఒక కొత్త ప్రాసెసర్ ప్లాట్ఫారమ్, కాబట్టి సాఫ్ట్వేర్ & ప్రోగ్రామింగ్ పరిసరాలకు చాలా తక్కువ మద్దతు ఉంది. | ARM చాలా పెద్ద ఆన్లైన్ కమ్యూనిటీని కలిగి ఉంది, ఇది మైక్రోప్రాసెసర్లు, మైక్రోకంట్రోలర్లు & సర్వర్ల వంటి వివిధ ప్లాట్ఫారమ్లలో టార్గెట్ డిజైనర్లకు సహాయం చేయడానికి లైబ్రరీలు & నిర్మాణాలకు మద్దతు ఇస్తుంది. |

| RISC V-ఆధారిత చిప్లు 1 వాట్ శక్తిని ఉపయోగిస్తాయి. | ARM-ఆధారిత చిప్లు 4 వాట్ల కంటే తక్కువ శక్తిని ఉపయోగిస్తాయి. |

| ఇది స్థిర & వేరియబుల్ ISA ఎన్కోడింగ్ సిస్టమ్ను కలిగి ఉంది. | ఇది స్థిరమైన ISA ఎన్కోడింగ్ వ్యవస్థను కలిగి ఉంది. |

| RISC V సూచనల సెట్ పరిమాణం 16-బిట్ నుండి 128-బిట్ల వరకు ఉంటుంది. | దీని సూచన పరిమాణం 16-బిట్ నుండి 64-బిట్ల వరకు ఉంటుంది. |

| ఇందులో 32 సాధారణ ప్రయోజనం & ఫ్లోటింగ్ పాయింట్ రిజిస్టర్లు ఉన్నాయి. | ఇందులో 31 సాధారణ ప్రయోజనం & ఫ్లోటింగ్ పాయింట్ రిజిస్టర్లు ఉన్నాయి. |

| ఇది 26-సింగిల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. | ఇది 33-సింగిల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. |

| ఇది 26-డబుల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. | ఇది 29-డబుల్ ప్రెసిషన్ ఫ్లోటింగ్ పాయింట్ ఆపరేషన్లను కలిగి ఉంది. |

RISC V వెరిలాగ్ కోడ్

RISC కోసం సూచన మెమరీ వెరిలాగ్ కోడ్ క్రింద చూపబడింది.

// RISC ప్రాసెసర్ కోసం వెరిలాగ్ కోడ్

// ఇన్స్ట్రక్షన్ మెమరీ కోసం వెరిలాగ్ కోడ్

మాడ్యూల్ ఇన్స్ట్రక్షన్_మెమరీ(

ఇన్పుట్[15:0] pc,

అవుట్పుట్[15:0] సూచన

);

reg [`col - 1:0] మెమరీ [`row_i - 1:0];

వైర్ [3 : 0] rom_addr = pc[4 : 1];

ప్రారంభ

ప్రారంభం

$readmemb(“./test/test.prog”, మెమరీ,0,14);

ముగింపు

బోధనను కేటాయించండి = మెమరీ[rom_addr];

ముగింపు మాడ్యూల్

16-బిట్ RISC V ప్రాసెసర్ కోసం వెరిలాగ్ కోడ్:

మాడ్యూల్ Risc_16_bit(

ఇన్పుట్ clk

);

వైర్ జంప్,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

వైర్[1:0] alu_op;

వైర్ [3:0] ఆప్కోడ్;

// డేటాపాత్

డేటాపాత్_యూనిట్ DU

(

.clk(clk),

.జంప్(జంప్),

.కప్ప(కప్ప),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.అలు_ఒప్(అలు_ఒప్),

.opcode(opcode)

);

// నియంత్రణ యూనిట్

కంట్రోల్_యూనిట్ నియంత్రణ

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.అలు_ఒప్(అలు_ఒప్),

.జంప్(జంప్),

.bne(bne),

.కప్ప(కప్ప),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

ముగింపు మాడ్యూల్

ఇన్స్ట్రక్షన్ సెట్స్

RISC V సూచనల సెట్లు క్రింద చర్చించబడ్డాయి.

అంకగణిత కార్యకలాపాలు

RISC V అంకగణిత కార్యకలాపాలు క్రింద ఇవ్వబడ్డాయి.

| జ్ఞాపకశక్తి | టైప్ చేయండి | సూచన | వివరణ |

| జోడించు rd, rs1, rs2 |

ఆర్ |

జోడించు | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

ఆర్ |

తీసివేయి | rdß rs1 – rs2 |

| ADDI RD, rs1, imm12 |

I |

వెంటనే జోడించండి | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

ఆర్ |

కంటే తక్కువ సెట్ చేయండి | rdß rs1 -< rs2 |

| SLTI RD, rs1, imm12 |

I |

తక్షణం కంటే తక్కువ సెట్ చేయండి | rdß rs1 -< imm12 |

| SLTU RD, rs1, rs2 |

ఆర్ |

సంతకం చేయని దాని కంటే తక్కువగా సెట్ చేయండి | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

I |

తక్షణ సంతకం చేయని దాని కంటే తక్కువ సెట్ చేయండి | rdß rs1 -< imm12 |

| LUI rd, imm20 |

IN |

వెంటనే ఎగువ లోడ్ చేయండి | rdß imm20<<12 |

| AUIP RD, imm20 |

IN |

PCకి వెంటనే ఎగువను జోడించండి | rdß PC+imm20<<12 |

లాజికల్ ఆపరేషన్స్

RISC V లాజికల్ ఆపరేషన్లు క్రింద ఇవ్వబడ్డాయి.

| జ్ఞాపకశక్తి | టైప్ చేయండి | సూచన | వివరణ |

| మరియు rd, rs1, rs2 |

ఆర్ |

మరియు | rdß rs1 & rs2 |

| OR RD, rs1, rs2 |

ఆర్ |

లేదా | rdß rs1 | రూ.2 |

| XOR rd, rs1, rs2 |

ఆర్ |

ఉచిత | rdß rs1 ^ rs2 |

| ANDI వ, rs1, imm12 |

I |

మరియు వెంటనే | rdß rs1 & imm2 |

| ORI RD, rs1, imm12 |

I |

లేదా తక్షణం | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

I |

వెంటనే XOR | rdß rs1 ^ rs2 |

| SLL RD, rs1, rs2 |

ఆర్ |

Shift లాజికల్ ఎడమ | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

ఆర్ |

కుడివైపుకి తార్కికంగా మారండి | rdß rs1 >> rs2 |

| RAS RD, rs1, rs2 |

ఆర్ |

కుడి అంకగణితాన్ని మార్చండి | rdß rs1 >> rs2 |

| SLLI RD, rs1, షామ్ట్ |

I |

Shift లాజికల్ తక్షణమే వదిలివేయబడింది | rdß rs1 << shamt |

| SRLI RD, rs1, షామ్ట్ |

I |

తక్షణమే కుడివైపుకి మార్చండి | rdß rs1 >> shamt |

| SRAI RD, rs1, షామ్ట్ |

I |

కుడి అంకగణితాన్ని వెంటనే మార్చండి | rdß rs1 >> shamt |

లోడ్/స్టోర్ కార్యకలాపాలు

RISC V లోడ్/స్టోర్ కార్యకలాపాలు క్రింద ఇవ్వబడ్డాయి.

| జ్ఞాపకశక్తి | టైప్ చేయండి | సూచన | వివరణ |

| LD rd, imm12 (rs1) |

I |

డబుల్ వర్డ్ లోడ్ చేయండి | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

I |

పదాన్ని లోడ్ చేయండి | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

I |

సగం లోడ్ చేయండి | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

I |

లోడ్ బైట్ | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

I |

లోడ్ వర్డ్ సంతకం చేయబడలేదు | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

I |

సగం పదం సంతకం చేయబడలేదు | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

I |

లోడ్ బైట్ సంతకం చేయబడలేదు | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

ఎస్ |

డబుల్ పదాన్ని నిల్వ చేయండి | rs2 నుండి మెమ్ [rs1 + imm12] |

| SW rs2, imm12 (rs1) |

ఎస్ |

స్టోర్ పదం | rs2 (31:0) నుండి నాకు [rs1 + imm12] |

| SH rs2, imm12 (rs1) |

ఎస్ |

సగం మార్గంలో నిల్వ చేయండి | rs2 (15:0) నుండి నాకు [rs1 + imm12] |

| SB rs2, imm12 (rs1) |

ఎస్ |

స్టోర్ బైట్ | rs2 (15:0) నుండి నాకు [rs1 + imm12] |

| SRAI RD, rs1, షామ్ట్ |

I |

కుడి అంకగణితాన్ని వెంటనే మార్చండి | rs2 (7:0) నుండి నాకు [rs1 +imm12] |

బ్రాంచింగ్ కార్యకలాపాలు

RISC V శాఖల కార్యకలాపాలు క్రింద ఇవ్వబడ్డాయి.

| జ్ఞాపకశక్తి | టైప్ చేయండి | సూచన | వివరణ |

| BEQ rs1, rs2, imm12 |

SB |

శాఖ సమానం | rs1== rs2 అయితే PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

శాఖ సమానంగా లేదు | rs1!= rs2 అయితే PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

బ్రాంచ్ కంటే ఎక్కువ లేదా సమానం | rs1>= rs2 అయితే PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

సంతకం చేయని దాని కంటే ఎక్కువ లేదా సమానమైన శాఖ | rs1>= rs2 అయితే PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

కంటే తక్కువ శాఖ | rs1< rs2 అయితే PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

సంతకం చేయని కంటే తక్కువ శాఖ | rs1< rs2 అయితే PC ß PC+imm12 <<1 |

| JAL RD, imm20 |

UJ |

జంప్ మరియు లింక్ | rdßPC+4 PCß PC+imm20 |

| JALR RD, imm12(rs1) |

I |

జంప్ మరియు లింక్ రిజిస్టర్ | rdßPC+4 PCß rs1+imm12 |

ప్రయోజనాలు

ది RISC యొక్క ప్రయోజనాలు V ప్రాసెసర్ కింది వాటిని చేర్చండి.

- RISCVని ఉపయోగించడం ద్వారా, మేము అభివృద్ధి సమయం, సాఫ్ట్వేర్ అభివృద్ధి, ధృవీకరణ మొదలైనవాటిని ఆదా చేయవచ్చు.

- ఈ ప్రాసెసర్లో సింప్లిసిటీ, ఓపెన్నెస్, మాడ్యులారిటీ, క్లీన్-స్లేట్ డిజైన్ మరియు ఎక్స్టెన్సిబిలిటీ వంటి అనేక ప్రోస్ ఉన్నాయి.

- దీనికి GCC (GNU కంపైలర్ కలెక్షన్), ఒక ఉచిత-సాఫ్ట్వేర్ కంపైలర్ వంటి అనేక భాషా కంపైలర్లు మద్దతు ఇస్తున్నాయి. Linux OS .

- ఎటువంటి రాయల్టీలు, లైసెన్సింగ్ ఫీజులు మరియు స్ట్రింగ్లు కనెక్ట్ చేయబడనందున కంపెనీలు దీన్ని ఉచితంగా ఉపయోగించవచ్చు.

- RISC-V ప్రాసెసర్ ఏ కొత్త లేదా వినూత్నమైన లక్షణాలను కలిగి ఉండదు ఎందుకంటే ఇది RISC యొక్క స్థాపించబడిన సూత్రాలను అనుసరిస్తుంది.

- అనేక ఇతర ISAల మాదిరిగానే, ఈ ప్రాసెసర్ స్పెసిఫికేషన్ వివిధ సూచనల సెట్ స్థాయిలను నిర్వచిస్తుంది. కాబట్టి ఇది 32 & 64-బిట్ వేరియంట్లతో పాటు ఫ్లోటింగ్ పాయింట్ సూచనలకు మద్దతునిచ్చే పొడిగింపులను కలిగి ఉంది.

- ఇవి ఉచితం, సరళమైనవి, మాడ్యులర్, స్థిరమైనవి మొదలైనవి.

ప్రతికూలతలు

ది RISC V ప్రాసెసర్ యొక్క ప్రతికూలతలు కింది వాటిని చేర్చండి.

- కాంప్లెక్స్ సూచనలను కంపైలర్లు & ప్రోగ్రామర్లు తరచుగా ఉపయోగిస్తారు.

- లూప్లోని తదుపరి సూచనలు అమలు కోసం మునుపటి సూచనలపై ఆధారపడి ఉన్నప్పుడు RISC యొక్క o/p కోడ్ ఆధారంగా మారవచ్చు.

- ఈ ప్రాసెసర్లు వివిధ రకాల సూచనలను వేగంగా సేవ్ చేయాలి, దీనికి సకాలంలో సూచనలకు ప్రతిస్పందించడానికి పెద్ద కాష్ మెమరీ సెట్ అవసరం.

- RISC యొక్క పూర్తి లక్షణాలు, సామర్థ్యాలు & ప్రయోజనాలు ప్రధానంగా ఆర్కిటెక్చర్పై ఆధారపడి ఉంటాయి.

అప్లికేషన్లు

ది RISC V యొక్క అప్లికేషన్లు ప్రాసెసర్ కింది వాటిని చేర్చండి.

- RISC-V ఎంబెడెడ్ సిస్టమ్స్, ఆర్టిఫిషియల్ ఇంటెలిజెన్స్ & మెషిన్ లెర్నింగ్లో ఉపయోగించబడుతుంది.

- ఈ ప్రాసెసర్లు అధిక-పనితీరు-ఆధారిత ఎంబెడెడ్ సిస్టమ్ అప్లికేషన్లలో ఉపయోగించబడతాయి.

- ఈ ప్రాసెసర్ ఎడ్జ్ కంప్యూటింగ్, AI & స్టోరేజ్ అప్లికేషన్ల వంటి కొన్ని నిర్దిష్ట ఫీల్డ్లలో ఉపయోగించడానికి తగినది.

- RISC-V ముఖ్యమైనది ఎందుకంటే ఇది చిన్న పరికర తయారీదారులను చెల్లించకుండా హార్డ్వేర్ను రూపొందించడానికి అనుమతిస్తుంది.

- ఈ ప్రాసెసర్ పరిశోధకులను మరియు డెవలపర్లను ఉచితంగా లభించే ISA లేదా ఇన్స్ట్రక్షన్ సెట్ ఆర్కిటెక్చర్తో డిజైన్ చేయడానికి మరియు పరిశోధన చేయడానికి అనుమతిస్తుంది.

- RISC V యొక్క అప్లికేషన్లు చిన్న ఎంబెడెడ్ మైక్రోకంట్రోలర్ల నుండి డెస్క్టాప్ PCలు & వెక్టర్ ప్రాసెసర్లతో సహా సూపర్ కంప్యూటర్ల వరకు ఉంటాయి.

అందువలన, ఇది RISC V ప్రాసెసర్ యొక్క అవలోకనం - ఆర్కిటెక్చర్, అప్లికేషన్లతో పని చేయడం. ఇక్కడ మీ కోసం ఒక ప్రశ్న ఉంది, CISC ప్రాసెసర్ అంటే ఏమిటి?