ది ఫీల్డ్-ఎఫెక్ట్ ట్రాన్సిస్టర్ (FET) ఒక ఎలక్ట్రానిక్ పరికరం, దీనిలో ఒక విద్యుత్ క్షేత్రం ప్రస్తుత ప్రవాహాన్ని నియంత్రించడానికి ఉపయోగిస్తారు. దీన్ని అమలు చేయడానికి పరికరం యొక్క గేట్ మరియు సోర్స్ టెర్మినల్స్ అంతటా సంభావ్య వ్యత్యాసం వర్తించబడుతుంది, ఇది కాలువ మరియు సోర్స్ టెర్మినల్స్ మధ్య వాహకతను మారుస్తుంది, దీనివల్ల ఈ టెర్మినల్స్ అంతటా నియంత్రిత ప్రవాహం ప్రవహిస్తుంది.

FET లను పిలుస్తారు యూనిపోలార్ ట్రాన్సిస్టర్లు ఎందుకంటే ఇవి సింగిల్-క్యారియర్-రకం పరికరాల వలె పనిచేయడానికి రూపొందించబడ్డాయి. మీరు వివిధ రకాల ఫీల్డ్ ఎఫెక్ట్ ట్రాన్సిస్టర్లను కనుగొంటారు.

చిహ్నం

N- ఛానల్ మరియు p- ఛానల్ JFET ల కొరకు గ్రాఫికల్ చిహ్నాలను ఈ క్రింది బొమ్మలలో చూడవచ్చు.

నేను దిశను సూచించడానికి n- ఛానల్ పరికరం కోసం లోపలికి సూచించే బాణం గుర్తులు మీరు స్పష్టంగా గమనించవచ్చుజి(గేట్ కరెంట్) p-n జంక్షన్ ముందుకు-పక్షపాతంగా ఉన్నప్పుడు ప్రవహించాల్సి ఉంటుంది.

పి-ఛానల్ పరికరం విషయంలో బాణం చిహ్నం దిశలో తేడా తప్ప పరిస్థితులు ఒకేలా ఉంటాయి.

FET మరియు BJT మధ్య వ్యత్యాసం

ఫీల్డ్-ఎఫెక్ట్ ట్రాన్సిస్టర్ (FET) అనేది మూడు-టెర్మినల్ పరికరం, ఇది విస్తృత శ్రేణి సర్క్యూట్ అనువర్తనాల కోసం రూపొందించబడింది, ఇది BJT ట్రాన్సిస్టర్ యొక్క గొప్ప స్థాయికి పూర్తి అవుతుంది.

మీరు BJT లు మరియు JFET ల మధ్య గణనీయమైన వ్యత్యాసాలను కనుగొంటారు, వాస్తవానికి అనేక సరిపోలిక లక్షణాలు ఉన్నాయి, వీటిని క్రింది చర్చలలో మాట్లాడతారు. ఈ పరికరాల మధ్య ప్రధాన వ్యత్యాసం అంజీర్ 5.1 ఎలో సూచించిన విధంగా ప్రస్తుత-నియంత్రిత పరికరం, అయితే జెఎఫ్ఇటి ట్రాన్సిస్టర్ అంజీర్ 5.1 బిలో సూచించిన విధంగా వోల్టేజ్-నియంత్రిత పరికరం.

ఒక్కమాటలో చెప్పాలంటే, ప్రస్తుత I.సిఅంజీర్లో 5.1a అనేది I స్థాయి యొక్క తక్షణ పనిబి. FET కోసం ప్రస్తుత I వోల్టేజ్ V యొక్క ఫంక్షన్జి.ఎస్అంజీర్ 5.1 బిలో చూపిన విధంగా ఇన్పుట్ సర్క్యూట్కు ఇవ్వబడింది.

రెండు సందర్భాల్లో, అవుట్పుట్ సర్క్యూట్ యొక్క ప్రవాహం ఇన్పుట్ సర్క్యూట్ యొక్క పరామితి ద్వారా నిర్వహించబడుతుంది. ఒక పరిస్థితిలో ప్రస్తుత స్థాయి మరియు మరొకటి అనువర్తిత వోల్టేజ్.

బైపోలార్ ట్రాన్సిస్టర్ల కోసం npn మరియు pnp మాదిరిగానే, మీరు n- ఛానల్ మరియు p- ఛానల్ ఫీల్డ్-ఎఫెక్ట్ ట్రాన్సిస్టర్లను కనుగొంటారు. కానీ, BJT ట్రాన్సిస్టర్ ఒక బైపోలార్ పరికరం అని మీరు గుర్తుంచుకోవాలి, ప్రసరణ ద్వి- ప్రసరణ స్థాయి రెండు ఛార్జ్ క్యారియర్లు, ఎలక్ట్రాన్లు మరియు రంధ్రాల పని అని సూచిస్తుంది.

మరోవైపు FET a యూనిపోలార్ పరికరం ఇది ఎలక్ట్రాన్ (ఎన్-ఛానల్) లేదా రంధ్రం (పి-ఛానల్) ప్రసరణపై ఆధారపడి ఉంటుంది.

'ఫీల్డ్-ఎఫెక్ట్' అనే పదబంధాన్ని ఈ విధంగా వివరించవచ్చు: ఎటువంటి భౌతిక సంబంధం లేకుండా అయస్కాంతం వైపు లోహ ఫైలింగ్లను ఆకర్షించడానికి శాశ్వత అయస్కాంతం యొక్క శక్తి మనందరికీ తెలుసు. FET లోపల చాలా సారూప్యంగా, నియంత్రణ మరియు నియంత్రిత పరిమాణాల మధ్య ప్రత్యక్ష సంబంధం లేకుండా అవుట్పుట్ సర్క్యూట్ యొక్క ప్రసరణ మార్గాన్ని ప్రభావితం చేసే ప్రస్తుత ఛార్జీల ద్వారా విద్యుత్ క్షేత్రం సృష్టించబడుతుంది. FET యొక్క అత్యంత కీలకమైన లక్షణాలలో ఒకటి దాని అధిక ఇన్పుట్ ఇంపెడెన్స్.

1 నుండి అనేక వందల మెగాహోమ్ల వరకు, ఇది బిజెటి కాన్ఫిగరేషన్ల యొక్క సాధారణ ఇన్పుట్ నిరోధక పరిధిని గణనీయంగా అధిగమిస్తుంది, ఇది లీనియర్ ఎసి యాంప్లిఫైయర్ మోడళ్లను అభివృద్ధి చేసేటప్పుడు చాలా ముఖ్యమైన లక్షణం.

అయినప్పటికీ, ఇన్పుట్ సిగ్నల్లోని వైవిధ్యాలకు BJT ఎక్కువ సున్నితత్వాన్ని కలిగి ఉంటుంది. అర్థం, అవుట్పుట్ కరెంట్ యొక్క మార్పు సాధారణంగా BJT లకు FET ల కంటే వారి ఇన్పుట్ వోల్టేజీలలో అదే మొత్తంలో మార్పు కోసం చాలా ఎక్కువ.

ఈ కారణంగా, FET లతో పోలిస్తే BJT యాంప్లిఫైయర్ల కొరకు ప్రామాణిక AC వోల్టేజ్ లాభాలు చాలా ఎక్కువ.

సాధారణంగా చెప్పాలంటే, FET లు BJT ల కంటే చాలా ఎక్కువ ఉష్ణ స్థితిస్థాపకంగా ఉంటాయి మరియు BJT లతో పోలిస్తే నిర్మాణంలో చిన్న పరిమాణంలో ఉంటాయి, ఇవి ఇంటిగ్రేటెడ్-సర్క్యూట్ (I) గా పొందుపరచడానికి ప్రత్యేకంగా అనుకూలంగా ఉంటాయి.సి)చిప్స్.

కొన్ని FET ల యొక్క నిర్మాణ లక్షణాలు, మరోవైపు, BJT ల కంటే శారీరక సంబంధాలకు అదనపు సున్నితంగా ఉండటానికి వీలు కల్పిస్తాయి.

మరిన్ని BJT / JFET సంబంధం

- ఒక బిజెటి విBE= 0.7 V దాని కాన్ఫిగరేషన్ యొక్క విశ్లేషణను ప్రారంభించడానికి ముఖ్యమైన అంశం.

- అదేవిధంగా, పరామితి I.జి= 0 A సాధారణంగా JFET సర్క్యూట్ యొక్క విశ్లేషణ కోసం పరిగణించబడే మొదటి విషయం.

- BJT కాన్ఫిగరేషన్ కోసం, I.బితరచుగా నిర్ణయించాల్సిన అవసరం ఉన్న మొదటి కారకం.

- అదేవిధంగా, JFET కొరకు, ఇది సాధారణంగా V.జి.ఎస్.

ఈ వ్యాసంలో మేము JFET లు లేదా జంక్షన్ ఫీల్డ్ ఎఫెక్ట్ ట్రాన్సిస్టర్లపై దృష్టి పెడతాము, తరువాతి వ్యాసంలో మెటల్-ఆక్సైడ్-సెమీకండక్టర్ ఫీల్డ్-ఎఫెక్ట్ ట్రాన్సిస్టర్ లేదా MOS-FET గురించి వివరిస్తాము.

JFET ల నిర్మాణం మరియు లక్షణాలు

మేము ఎర్లీట్ నేర్చుకున్నట్లు ఒక JFET కి 3 లీడ్స్ ఉన్నాయి. వాటిలో ఒకటి ఇతర రెండింటి మధ్య ప్రస్తుత ప్రవాహాన్ని నియంత్రిస్తుంది.

BJT ల మాదిరిగానే, JFET లలో కూడా n- ఛానల్ పరికరం p- ఛానల్ ప్రతిరూపాల కంటే ఎక్కువగా ఉపయోగించబడుతుంది, ఎందుకంటే n పరికరాలు p- పరికరంతో పోలిస్తే మరింత సమర్థవంతంగా మరియు వినియోగదారు స్నేహపూర్వకంగా ఉంటాయి.

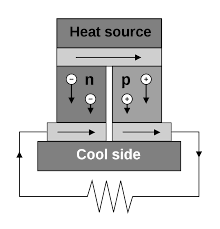

కింది చిత్రంలో మనం n- ఛానల్ JFET యొక్క ప్రాథమిక నిర్మాణం లేదా నిర్మాణాన్ని చూడవచ్చు. N- రకం కూర్పు p- రకం పొరలలో ప్రధాన ఛానెల్ను ఏర్పరుస్తుందని మనం చూడవచ్చు.

N- రకం ఛానెల్ యొక్క ఎగువ భాగం కాలువ (D) అనే టెర్మినల్తో ఓహ్మిక్ పరిచయం ద్వారా కలుస్తుంది, అదే ఛానెల్ యొక్క దిగువ విభాగం కూడా మూలం (S) అనే మరొక టెర్మినల్తో ఓహ్మిక్ పరిచయం ద్వారా అనుసంధానించబడి ఉంది.

పి-రకం పదార్థాల జంట గేట్ (జి) గా సూచించబడే టెర్మినల్తో కలిసి ఉంటుంది. ముఖ్యంగా కాలువ మరియు సోర్స్ టెర్మినల్స్ n- రకం ఛానల్ చివరలను కలుపుతున్నాయని మేము కనుగొన్నాము. గేట్ టెర్మినల్ ఒక జత పి-ఛానల్ మెటీరియల్తో జతచేయబడుతుంది.

Jfet అంతటా వోల్టేజ్ వర్తించనప్పుడు, దాని రెండు p-n జంక్షన్లు ఎటువంటి పక్షపాత పరిస్థితులు లేకుండా ఉంటాయి. ఈ పరిస్థితిలో పైన పేర్కొన్న చిత్రంలో సూచించినట్లుగా ప్రతి జంక్షన్లో క్షీణత ప్రాంతం ఉంది, ఇది ఎటువంటి పక్షపాతం లేకుండా డయోడ్ పి-ఎన్ ప్రాంతం వలె కనిపిస్తుంది.

నీటి సారూప్యత

JFET యొక్క పని మరియు నియంత్రణ కార్యకలాపాలను ఈ క్రింది నీటి సారూప్యత ద్వారా అర్థం చేసుకోవచ్చు.

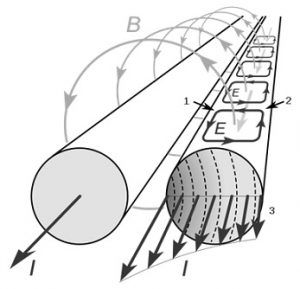

ఇక్కడ, నీటి పీడనాన్ని కాలువ నుండి మూలం వైపు అనువర్తిత వోల్టేజ్ మాగ్నిట్యూడ్తో పోల్చవచ్చు.

నీటి ప్రవాహాన్ని ఎలక్ట్రాన్ల ప్రవాహంతో పోల్చవచ్చు. ట్యాప్ యొక్క నోరు JFET యొక్క సోర్స్ టెర్మినల్ను అనుకరిస్తుంది, అయితే ట్యాప్ యొక్క ఎగువ భాగం నీరు బలవంతంగా ఉన్న చోట JFET యొక్క కాలువను వర్ణిస్తుంది.

ట్యాప్ నాబ్ JFET యొక్క గేట్ లాగా పనిచేస్తుంది. ట్యాప్ నాబ్ నోరు తెరిచేటప్పుడు నీటి ప్రవాహాన్ని నియంత్రిస్తున్నట్లే, ఇన్పుట్ సంభావ్యత సహాయంతో ఇది కాలువ నుండి మూలానికి ఎలక్ట్రాన్ల (ఛార్జ్) ప్రవాహాన్ని నియంత్రిస్తుంది.

JFET నిర్మాణం నుండి, కాలువ మరియు సోర్స్ టెర్మినల్స్ n- ఛానల్ యొక్క వ్యతిరేక చివరలలో ఉన్నాయని మనం చూడవచ్చు మరియు ఈ పదం ఎలక్ట్రాన్ ప్రవాహం ఆధారంగా ఉన్నందున మనం వ్రాయవచ్చు:

విజి.ఎస్= 0 వి, విడి.ఎస్కొన్ని సానుకూల విలువ

అంజీర్ 5.4 లో మనం పాజిటివ్ వోల్టేజ్ V ని చూడవచ్చుడి.ఎస్n- ఛానెల్ అంతటా వర్తించబడుతుంది. V అనే షరతును సృష్టించడానికి గేట్ టెర్మినల్ నేరుగా మూలానికి చేరిందిజి.ఎస్= 0 వి. ఇది గేట్ మరియు సోర్స్ టెర్మినల్స్ ఒకే సంభావ్యతతో ఉండటానికి వీలు కల్పిస్తుంది మరియు ప్రతి పి-మెటీరియల్ యొక్క తక్కువ ముగింపు క్షీణత ప్రాంతానికి దారి తీస్తుంది, పైన పేర్కొన్న మొదటి రేఖాచిత్రంలో మనం పక్షపాతం లేని స్థితితో చూస్తాము.

వోల్టేజ్ V. వెంటనేడిడి(= విడి.ఎస్) వర్తించబడుతుంది, ఎలక్ట్రాన్లు కాలువ టెర్మినల్ వైపుకు లాగబడతాయి, ప్రస్తుత ID యొక్క సాంప్రదాయిక ప్రవాహాన్ని ఉత్పత్తి చేస్తాయి, అంజీర్ 5.4 లో సూచించినట్లు.

చార్జ్ యొక్క ప్రవాహం యొక్క దిశ కాలువ మరియు మూల ప్రవాహం పరిమాణంలో సమానంగా ఉంటుందని తెలుపుతుంది (Iడి= నేనుఎస్). అంజీర్ 5.4 లో చిత్రీకరించిన షరతుల ప్రకారం, ఛార్జ్ యొక్క ప్రవాహం చాలా అనియంత్రితంగా కనిపిస్తుంది మరియు కాలువ మరియు మూలం మధ్య n- ఛానల్ యొక్క నిరోధకత ద్వారా మాత్రమే ప్రభావితమవుతుంది.

రెండు p- రకం పదార్థాల ఎగువ విభాగం చుట్టూ క్షీణత ప్రాంతం పెద్దదిగా ఉందని మీరు గమనించవచ్చు. ప్రాంతం యొక్క పరిమాణంలో ఈ వ్యత్యాసం అంజీర్ 5.5 ద్వారా ఆదర్శంగా వివరించబడింది. N- ఛానెల్లో ఏకరీతి నిరోధకత ఉందని imagine హించుకుందాం, ఇది అంజీర్ 5.5 లో సూచించిన విభాగాలకు విభజించబడుతుంది.

ప్రస్తుత నేనుడిఅదే చిత్రంలో చూపిన విధంగా ఛానెల్ ద్వారా వోల్టేజ్ శ్రేణులను నిర్మించవచ్చు. ఫలితంగా, p- రకం పదార్థం యొక్క ఎగువ ప్రాంతం సుమారు 1.5 V స్థాయి ద్వారా రివర్స్ పక్షపాతంతో ఉంటుంది, దిగువ ప్రాంతం కేవలం 0.5 V ద్వారా రివర్స్-బయాస్డ్ అవుతుంది.

మొత్తం ఛానెల్ వెంట p-n జంక్షన్ రివర్స్-బయాస్డ్ అయిన పాయింట్ అదే చిత్రంలో చూపిన విధంగా సున్నా ఆంపియర్లతో గేట్ కరెంట్కు దారితీస్తుంది. ఈ లక్షణం నాకు దారితీస్తుందిజి= 0 A అనేది JFET యొక్క ముఖ్యమైన లక్షణం.

విడి.ఎస్సంభావ్యత 0 నుండి కొన్ని వోల్ట్లకు పెరుగుతుంది, ఓం యొక్క చట్టం మరియు I యొక్క ప్లాట్లు ప్రకారం ప్రస్తుత పెరుగుదల పెరుగుతుందిడి5 వ పంక్తిడి.ఎస్అంజీర్ 5.6 లో నిరూపించబడినట్లు చూడవచ్చు.

ప్లాటింగ్ యొక్క తులనాత్మక సరళత V యొక్క తక్కువ విలువ ప్రాంతాలకు చూపిస్తుందిడి.ఎస్, నిరోధకత ప్రాథమికంగా ఏకరీతిగా ఉంటుంది. విడి.ఎస్అంజీర్ 5.6 లో VP అని పిలువబడే స్థాయికి చేరుకుంటుంది మరియు దగ్గరగా ఉంటుంది, అంజీర్ 5.4 లో ఇచ్చిన విధంగా క్షీణత ప్రాంతాలు విస్తరిస్తాయి.

ఇది ఛానెల్ వెడల్పు స్పష్టంగా తగ్గుతుంది. తగ్గిన ప్రసరణ మార్గం అంజీర్ 5.6 యొక్క వక్రతకు దారితీసే ప్రతిఘటన పెరుగుదలకు దారితీస్తుంది.

వక్రరేఖ మరింత క్షితిజ సమాంతరంగా ఉంటుంది, ప్రతిఘటన అధికంగా ఉంటుంది, ఇది ప్రతిఘటన సమాంతర ప్రాంతంలో “అనంతమైన” ఓంల వైపుకు వస్తున్నట్లు సూచిస్తుంది. ఎప్పుడు విడి.ఎస్అంజీర్ 5.7 లో చూపిన విధంగా రెండు క్షీణత ప్రాంతాలు “సంప్రదించవచ్చు” అని కనిపించే మేరకు పెరుగుతుంది, ఇది చిటికెడు-ఆఫ్ అని పిలువబడే పరిస్థితికి దారితీస్తుంది.

వి ద్వారా మొత్తండి.ఎస్ఈ పరిస్థితిని అభివృద్ధి చేస్తుంది చిటికెడు-ఆఫ్ వోల్టేజ్ మరియు ఇది V చే సూచించబడుతుందిపిఅంజీర్ 5.6 లో చూపినట్లు. సాధారణంగా, చిటికెడు-ఆఫ్ అనే పదం తప్పుదారి పట్టించేది ఎందుకంటే ఇది ప్రస్తుత I ని సూచిస్తుందిడి'పించ్డ్ ఆఫ్' మరియు 0 A. కి వస్తుంది. అంజీర్ 5.6 లో నిరూపించబడినట్లుగా, ఈ సందర్భంలో ఇది స్పష్టంగా కనబడదు. నేనుడినేను వర్గీకరించిన సంతృప్త స్థాయిని కలిగి ఉంటుందిడిఎస్ఎస్అంజీర్ 5.6 లో.

నిజం చాలా తక్కువ ఛానెల్ ఉనికిలో ఉంది, గణనీయంగా అధిక సాంద్రతతో.

ID వద్ద డ్రాప్ చేయని పాయింట్ చిటికెడు-ఆఫ్ మరియు అంజీర్ 5.6 లో సూచించిన విధంగా సంతృప్త స్థాయిని సంరక్షిస్తుంది.

కాలువ ప్రవాహం లేనందున, p-n జంక్షన్ వెంట మారుతున్న రివర్స్ బయాస్ మొత్తాన్ని నిర్ణయించడానికి n- ఛానల్ పదార్థం ద్వారా విభిన్న సంభావ్య స్థాయిల యొక్క అవకాశాన్ని తొలగిస్తుంది. తుది ఫలితం ప్రేరేపించిన క్షీణత ప్రాంత పంపిణీని కోల్పోవడం చిటికెడు-ఆఫ్ మొదలు పెట్టుటకు.

మేము V ని పెంచుతున్నప్పుడుడి.ఎస్V పైనపి, రెండు క్షీణత ప్రాంతాలు ఒకదానితో ఒకటి ఛానెల్ వెంట పొడవు పెరుగుదలను ఎదుర్కొనే దగ్గరి సంప్రదింపు ప్రాంతం. అయితే ID స్థాయి తప్పనిసరిగా మారదు.

ఆ విధంగా క్షణం విడి.ఎస్V కంటే ఎక్కువp, JFET ప్రస్తుత మూలం యొక్క లక్షణాలను పొందుతుంది.

JFET లో అంజీర్ 5.8 లో నిరూపించబడినట్లు I వద్ద నిర్ణయించబడుతుందిడి= నేనుడిఎస్ఎస్, కానీ వోల్టేజ్ V.డి.ఎస్VP కన్నా ఎక్కువ కనెక్ట్ చేయబడిన లోడ్ ద్వారా స్థాపించబడింది.

IDSS సంజ్ఞామానం యొక్క ఎంపిక గేట్ నుండి సోర్స్ వరకు షార్ట్ సర్క్యూట్ లింక్ కలిగి ఉన్న డ్రెయిన్ టు సోర్స్ కరెంట్ అనే దానిపై ఆధారపడి ఉంటుంది.

తదుపరి పరిశోధన మాకు ఈ క్రింది మూల్యాంకనాన్ని ఇస్తుంది:

నేనుడిఎస్ఎస్ఇది JFET కొరకు అత్యధిక కాలువ ప్రవాహం మరియు ఇది V పరిస్థితుల ద్వారా స్థాపించబడిందిజి.ఎస్= 0 V మరియు V.డి.ఎస్> | విపి |.

అంజీర్ 5.6 V లో గమనించండిజి.ఎస్వక్రరేఖ యొక్క పూర్తి విస్తరణకు 0 వి. కింది విభాగాలలో, అంజీర్ 5.6 గుణాలు V స్థాయిగా ఎలా ప్రభావితమవుతాయో నేర్చుకుంటాముజి.ఎస్వైవిధ్యమైనది.

విజి.ఎస్ <0V

గేట్ మరియు మూలం అంతటా వర్తించే అస్థిరత VGS గా సూచించబడుతుంది, ఇది JFET కార్యకలాపాలను నియంత్రించడానికి బాధ్యత వహిస్తుంది.

నేను BJT యొక్క ఉదాహరణను తీసుకుంటే, నేను యొక్క వక్రతలు వలెసిvs విఇదిI యొక్క వివిధ స్థాయిలకు నిర్ణయించబడతాయిబి, అదేవిధంగా I యొక్క వక్రతలుడిvs విడి.ఎస్V యొక్క వివిధ స్థాయిలకుజి.ఎస్JFET కౌంటర్ కోసం సృష్టించవచ్చు.

దీని కోసం గేట్ టెర్మినల్ సోర్స్ పొటెన్షియల్ స్థాయి కంటే తక్కువ తక్కువ సంభావ్యత వద్ద సెట్ చేయబడింది.

దిగువ Fig.5.9 ను సూచిస్తూ, తగ్గిన V కోసం గేట్ / సోర్స్ టెర్మినల్స్ అంతటా -1V వర్తించబడుతుందిడి.ఎస్స్థాయి.

ప్రతికూల సంభావ్య పక్షపాతం యొక్క లక్ష్యం V.జి.ఎస్V యొక్క పరిస్థితిని పోలి ఉండే క్షీణత ప్రాంతాలను అభివృద్ధి చేయడంజి.ఎస్= 0, కానీ గణనీయంగా తగ్గిన V వద్దడి.ఎస్.

దీనివల్ల గేట్ తక్కువ స్థాయి V తో సంతృప్త బిందువును పొందుతుందిడి.ఎస్అంజీర్ 5.10 (విజి.ఎస్= -1 వి).

I కోసం సంబంధిత సంతృప్త స్థాయిడితగ్గించినట్లు కనుగొనవచ్చు మరియు వాస్తవానికి V గా తగ్గుతుందిజి.ఎస్మరింత ప్రతికూలంగా ఉంటుంది.

చిటికెడు-ఆఫ్ వోల్టేజ్ V వలె పారాబొలిక్ ఆకారంతో పడిపోవడాన్ని మీరు అంజీర్ 5.10 లో స్పష్టంగా చూడవచ్చుజి.ఎస్మరింత ప్రతికూలంగా ఉంటుంది.

చివరగా, విజి.ఎస్= -విp, చివరికి 0 mA అయిన సంతృప్త స్థాయిని స్థాపించడానికి ఇది తగినంత ప్రతికూలతను పొందుతుంది. ఈ స్థాయిలో, JFET పూర్తిగా 'ఆఫ్ చేయబడింది'.

V యొక్క స్థాయిజి.ఎస్ఇది నాకు కారణమవుతుందిడి0 mA ని చేరుకోవడానికి V ద్వారా వర్గీకరించబడుతుందిజి.ఎస్= విపి, ఇందులో విపిn- ఛానల్ పరికరాలకు ప్రతికూల వోల్టేజ్ మరియు p- ఛానల్ JFET లకు సానుకూల వోల్టేజ్.

సాధారణంగా, మీరు చూపించే చాలా JFET డేటాషీట్లను కనుగొనవచ్చు చిటికెడు-ఆఫ్ వోల్టేజ్ V గా పేర్కొనబడిందిGS (ఆఫ్)V కి బదులుగాపి.

పై చిత్రంలో చిటికెడు-లోకస్ యొక్క కుడి వైపున ఉన్న ప్రాంతం సాంప్రదాయకంగా వక్రీకరణ ఉచిత సిగ్నల్ సాధించడానికి సరళ యాంప్లిఫైయర్లలో ఉపయోగించబడుతుంది. ఈ ప్రాంతాన్ని సాధారణంగా పిలుస్తారు స్థిరమైన-ప్రస్తుత, సంతృప్త లేదా సరళ విస్తరణ ప్రాంతం.

వోల్టేజ్-నియంత్రిత రెసిస్టర్

అదే చిత్రంలో చిటికెడు-లోకస్ యొక్క ఎడమ వైపున ఉన్న ప్రాంతాన్ని అంటారు ఓమిక్ ప్రాంతం లేదా వోల్టేజ్-నియంత్రిత నిరోధక ప్రాంతం.

ఈ ప్రాంతంలో పరికరం వాస్తవానికి వేరియబుల్ రెసిస్టర్గా పనిచేస్తుంది (ఉదాహరణకు ఆటోమేటిక్ గెయిన్ కంట్రోల్ అప్లికేషన్లో), దాని నిరోధకత అనువర్తిత గేట్ / సోర్స్ సంభావ్యత ద్వారా నియంత్రించబడుతుంది.

V కోసం JFET యొక్క కాలువ / మూల నిరోధకతను కూడా సూచించే ప్రతి వక్రత యొక్క వాలు మీరు చూడవచ్చుడి.ఎస్

మేము ప్రతికూల సామర్థ్యంతో VGS ను అధికం చేస్తున్నప్పుడు, ప్రతి వక్రత యొక్క వాలు మరింత అడ్డంగా ఉంటుంది, దామాషా ప్రకారం పెరుగుతున్న నిరోధక స్థాయిలను ప్రదర్శిస్తుంది.

కింది సమీకరణం ద్వారా, VGS వోల్టేజ్కు సంబంధించి ప్రతిఘటన స్థాయికి మంచి ప్రారంభ అంచనాను పొందగలుగుతున్నాము.

p- ఛానల్ JFET వర్కింగ్

పి-ఛానల్ JFET యొక్క అంతర్గత లేఅవుట్ మరియు నిర్మాణం ఖచ్చితంగా n- ఛానల్ ప్రతిరూపానికి సమానంగా ఉంటుంది, p- మరియు n- రకం పదార్థాల ప్రాంతాలు రివర్స్ చేయబడతాయి తప్ప, క్రింద చూపిన విధంగా:

వోల్టేజ్ VGS మరియు VDS యొక్క వాస్తవ ధ్రువణతలతో పాటు, ప్రస్తుత ప్రవాహం యొక్క దిశలను కూడా రివర్స్ చేసినట్లు చూడవచ్చు. పి-ఛానల్ JFET విషయంలో, గేట్ / మూలం అంతటా సానుకూల సామర్థ్యాన్ని పెంచడానికి ప్రతిస్పందనగా ఛానెల్ నిర్బంధించబడుతుంది.

V కోసం డబుల్ సబ్స్క్రిప్ట్తో సంజ్ఞామానండి.ఎస్V కోసం ప్రతికూల వోల్టేజ్కు దారి తీస్తుందిడి.ఎస్, Fig.5.12 యొక్క లక్షణాలపై చూపిన విధంగా. ఇక్కడ, మీరు నన్ను కనుగొనవచ్చుడిఎస్ఎస్6 mA వద్ద, V వద్ద చిటికెడు-ఆఫ్ వోల్టేజ్జి.ఎస్= + 6 వి.

V కోసం నీ మైనస్ గుర్తు ఉన్నందున దయచేసి అబ్బురపడకండిడి.ఎస్. మూలం కాలువ కంటే ఎక్కువ సామర్థ్యాన్ని కలిగి ఉందని ఇది సూచిస్తుంది.

అధిక V కోసం వక్రతలు మీరు చూడవచ్చుడి.ఎస్స్థాయిలు అకస్మాత్తుగా అనియంత్రితంగా కనిపించే విలువలకు పెరుగుతాయి. నిలువుగా సూచించబడిన పెరుగుదల విచ్ఛిన్న పరిస్థితిని సూచిస్తుంది, అనగా ఛానెల్ పరికరం ద్వారా ప్రస్తుతము ఈ సమయంలో బాహ్య సర్క్యూట్రీ ద్వారా పూర్తిగా నియంత్రించబడుతుంది.

ఎన్-ఛానల్ పరికరం కోసం ఇది Fig.5.10 లో స్పష్టంగా కనిపించనప్పటికీ, ఇది తగినంత అధిక వోల్టేజ్ కింద అవకాశం కావచ్చు.

V ఉంటే ఈ ప్రాంతాన్ని తొలగించవచ్చుDS (గరిష్టంగా)పరికరం యొక్క డేటాషీట్ నుండి గుర్తించబడింది మరియు పరికరం అసలు V వలె కాన్ఫిగర్ చేయబడిందిడి.ఎస్ఏదైనా V కి ఈ గుర్తించబడిన విలువ కంటే విలువ తక్కువగా ఉంటుందిజి.ఎస్.

మునుపటి: 5 ఉత్తమ 40 వాట్ యాంప్లిఫైయర్ సర్క్యూట్లు అన్వేషించబడ్డాయి తర్వాత: 2N3055 డేటాషీట్, పిన్అవుట్, అప్లికేషన్ సర్క్యూట్లు