యాంప్లిఫైయర్ సర్క్యూట్ల తయారీకి ట్రాన్సిస్టర్లు (బిజెటిలు) ప్రముఖంగా ఉపయోగించబడుతున్నప్పటికీ, అనువర్తనాలను మార్చడానికి కూడా వీటిని సమర్థవంతంగా ఉపయోగించవచ్చు.

ట్రాన్సిస్టర్ స్విచ్ ఒక సర్క్యూట్, దీనిలో ట్రాన్సిస్టర్ యొక్క కలెక్టర్ దాని బేస్ ఉద్గారిణి వద్ద తక్కువ కరెంట్ ఆన్ / ఆఫ్ సిగ్నల్కు అనుగుణంగా ప్రతిస్పందనగా సాపేక్షంగా పెద్ద కరెంట్తో ఆన్ / ఆఫ్ చేయబడుతుంది.

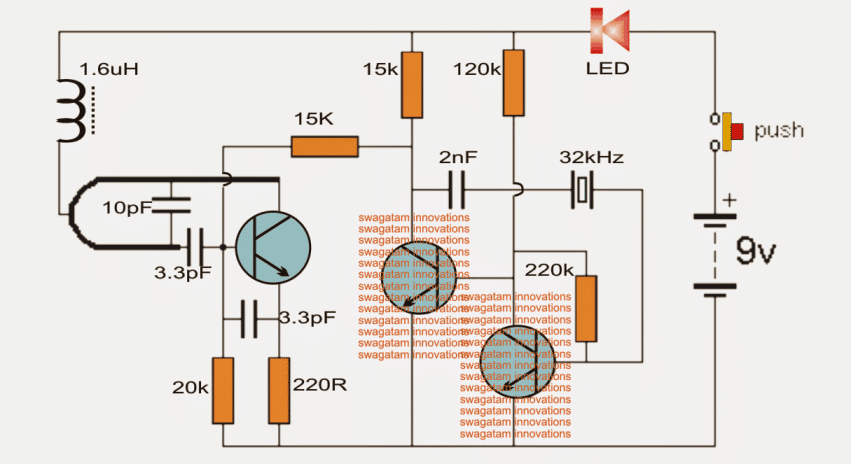

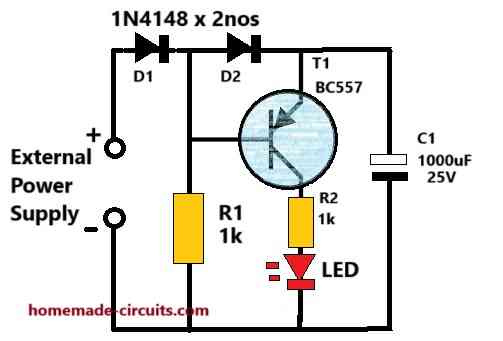

ఉదాహరణగా, కిందివి BJT కాన్ఫిగరేషన్ను స్విచ్గా ఉపయోగించవచ్చు కంప్యూటర్ లాజిక్ సర్క్యూట్ కోసం ఇన్పుట్ సిగ్నల్ విలోమం కోసం.

అవుట్పుట్ వోల్టేజ్ Vc ట్రాన్సిస్టర్ యొక్క బేస్ / ఉద్గారిణి అంతటా వర్తించే సామర్థ్యానికి విరుద్ధంగా ఉందని ఇక్కడ మీరు కనుగొనవచ్చు.

అలాగే, యాంప్లిఫైయర్ ఆధారిత సర్క్యూట్ల మాదిరిగా కాకుండా, ఏదైనా స్థిర DC మూలంతో బేస్ కనెక్ట్ కాలేదు. కలెక్టర్ సిస్టమ్ యొక్క సరఫరా స్థాయిలకు అనుగుణంగా ఉండే DC మూలాన్ని కలిగి ఉంది, ఉదాహరణకు ఈ కంప్యూటర్ అప్లికేషన్ కేసులో 5 V మరియు 0 V.

కింది చిత్రంలో చూపిన విధంగా ఆపరేటింగ్ పాయింట్ కట్ ఆఫ్ నుండి లోడ్ రేఖ వెంట సంతృప్తతకు సరిగ్గా మారుతుందని నిర్ధారించడానికి ఈ వోల్టేజ్ విలోమం ఎలా రూపొందించబడుతుందనే దాని గురించి మేము మాట్లాడుతాము:

ప్రస్తుత దృష్టాంతంలో, పైన పేర్కొన్న చిత్రంలో IC = ICEO = 0 mA, IB = 0 uA ఉన్నప్పుడు (నిర్మాణ వ్యూహాలను పెంచడానికి సంబంధించి గొప్ప అంచనా). అదనంగా, సాధారణ 0.1 నుండి 0.3 V స్థాయికి బదులుగా VCE = VCE (sat) = 0 V అని అనుకుందాం.

ఇప్పుడు, Vi = 5 V వద్ద BJT ఆన్ అవుతుంది, మరియు డిజైన్ పరిశీలన ఆకృతీకరణ అత్యంత సంతృప్తమైందని నిర్ధారించుకోవాలి, IB యొక్క పరిమాణం ద్వారా, ఇది సంతృప్త స్థాయికి దగ్గరగా కనిపించే IB వక్రతతో సంబంధం ఉన్న విలువ కంటే ఎక్కువగా ఉండవచ్చు.

పై చిత్రంలో తెలివిగా చెప్పవచ్చు, ఈ పరిస్థితులు IB 50 uA కన్నా ఎక్కువగా ఉండాలని పిలుస్తాయి.

సంతృప్త స్థాయిలను లెక్కిస్తోంది

చూపిన సర్క్యూట్ కోసం కలెక్టర్ సంతృప్త స్థాయిని సూత్రాన్ని ఉపయోగించి లెక్కించవచ్చు:

IC (sat) = Vcc / Rc

సంతృప్త స్థాయికి ముందు క్రియాశీల ప్రాంతంలో బేస్ కరెంట్ యొక్క పరిమాణాన్ని సూత్రాన్ని ఉపయోగించి లెక్కించవచ్చు:

IB (గరిష్టంగా) ≅ IC (sat) / βdc ---------- సమీకరణం 1

ఇది సంతృప్త స్థాయిని అమలు చేయడానికి, కింది షరతును తప్పక తీర్చాలని సూచిస్తుంది:

IB> IC (sat) / IC (sat) / βdc -------- సమీకరణం 2

పైన చర్చించిన గ్రాఫ్లో, Vi = 5 V ఉన్నప్పుడు, ఫలిత IB స్థాయిని ఈ క్రింది పద్ధతిలో అంచనా వేయవచ్చు:

ఈ ఫలితాలతో సమీకరణం 2 ను పరీక్షిస్తే మనకు లభిస్తుంది:

ఇది అవసరమైన పరిస్థితిని సంపూర్ణంగా సంతృప్తిపరిచినట్లు కనిపిస్తుంది. నిస్సందేహంగా, 60 uA కన్నా ఎక్కువ IB యొక్క ఏదైనా విలువ నిలువు అక్షానికి చాలా దగ్గరగా ఉన్న లోడ్ రేఖపై Q- పాయింట్ అంతటా ప్రవేశించడానికి అనుమతించబడుతుంది.

ఇప్పుడు, మొదటి రేఖాచిత్రంలో చూపిన BJT నెట్వర్క్ను సూచిస్తూ, Vi = 0 V, IB = 0 uA, మరియు IC = ICEO = 0 mA ను uming హిస్తే, RC అంతటా సంభవించే అస్థిరత డ్రాప్ సూత్రం ప్రకారం ఉంటుంది:

VRC = ICRC = 0 V.

ఇది పై మొదటి రేఖాచిత్రం కోసం మాకు VC = +5 V ఇస్తుంది.

కంప్యూటర్ లోగో స్విచ్చింగ్ అనువర్తనాలతో పాటు, ఈ BJT కాన్ఫిగరేషన్ కూడా లోడ్ లైన్ యొక్క అదే తీవ్రమైన పాయింట్లను ఉపయోగించి స్విచ్ లాగా అమలు చేయవచ్చు.

సంతృప్తత జరిగినప్పుడు, ప్రస్తుత ఐసి చాలా ఎక్కువగా ఉంటుంది, ఇది వోల్టేజ్ VCE ను అత్యల్ప స్థానానికి పడిపోతుంది.

ఇది క్రింది టెర్మినల్లో చిత్రీకరించిన విధంగా రెండు టెర్మినల్లలో ప్రతిఘటన స్థాయికి దారితీస్తుంది మరియు క్రింది సూత్రాన్ని ఉపయోగించి లెక్కించబడుతుంది:

కింది చిత్రంలో సూచించిన విధంగా R (sat) = VCE (sat) / IC (sat).

పై సూత్రంలో 0.15 V వంటి VCE (sat) కోసం మేము ఒక సాధారణ సగటు విలువను If హిస్తే, మనకు లభిస్తుంది:

BJT యొక్క కలెక్టర్ టెర్మినల్స్ వద్ద కిలో ఓంస్లో సిరీస్ నిరోధకతతో పోల్చినప్పుడు కలెక్టర్ ఉద్గారిణి టెర్మినల్స్ అంతటా ఈ నిరోధక విలువ చాలా తక్కువగా కనిపిస్తుంది.

ఇప్పుడు, Vi = 0 V ఇన్పుట్ చేసినప్పుడు, కలెక్టర్ ఉద్గారిణి అంతటా నిరోధకత ఏర్పడటానికి BJT మారడం కత్తిరించబడుతుంది:

R (కటాఫ్) = Vcc / ICEO = 5 V / 0 mA =

ఇది కలెక్టర్ ఉద్గారిణి టెర్మినల్స్ అంతటా ఓపెన్ సర్క్యూట్ రకమైన పరిస్థితికి దారితీస్తుంది. ICEO కోసం ఒక సాధారణ విలువ 10 uA ను మేము పరిగణించినట్లయితే, కట్ ఆఫ్ నిరోధకత యొక్క విలువ క్రింద ఇవ్వబడింది:

Rcutoff = Vcc / ICEO = 5 V / 10 uA = 500 k

ఈ విలువ గణనీయంగా పెద్దదిగా కనిపిస్తుంది మరియు చాలా BJT కాన్ఫిగరేషన్ కోసం స్విచ్ వలె ఓపెన్ సర్క్యూట్కు సమానం.

ప్రాక్టికల్ ఉదాహరణను పరిష్కరించడం

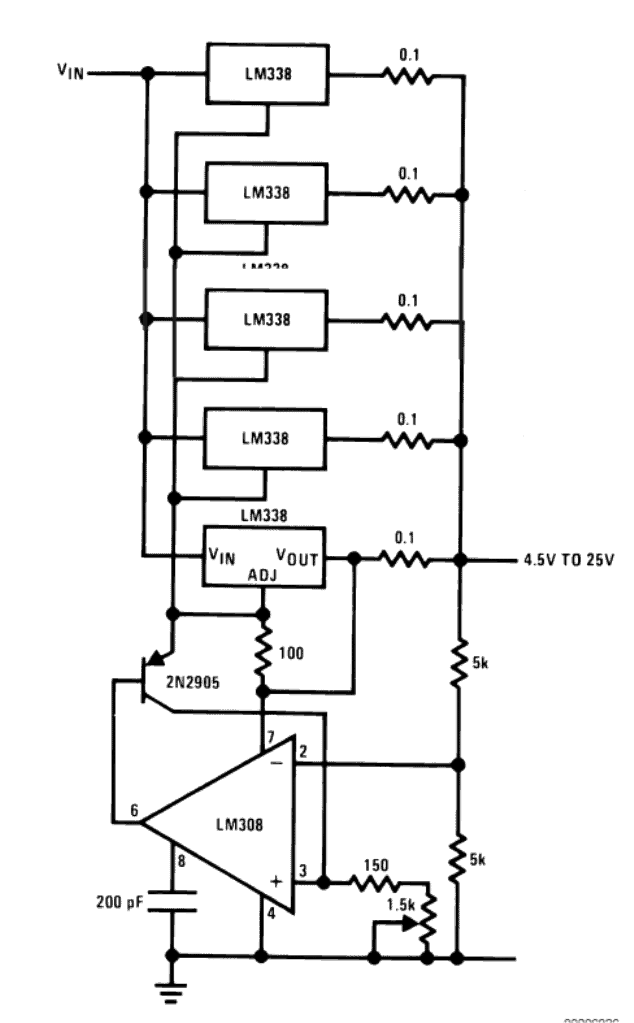

దిగువ ఇన్వర్టర్ లాగా కాన్ఫిగర్ చేయబడిన ట్రాన్సిస్టర్ స్విచ్ కోసం RB మరియు RC యొక్క విలువలను లెక్కించండి, ICmax = 10mA

కలెక్టర్ సంతృప్తిని వ్యక్తీకరించే సూత్రం:

ICsat = Vcc / Rc

10 mA = 10 V / Rc

Rc = 10 V / 10 mA = 1 kΩ

అలాగే, సంతృప్త సమయంలో

IB IC (sat) / βdc = 10 mA / 250 = 40 μA

హామీ సంతృప్తత కోసం IB = 60 μA ను ఎంచుకుందాం, మరియు సూత్రాన్ని ఉపయోగించడం ద్వారా

IB = Vi - 0.7 V / RB, మనకు లభిస్తుంది

RB = 10 V - 0.7 V / 60 μA = 155 kΩ,

పై ఫలితాన్ని 150 kΩ కి చుట్టుముట్టడం మరియు పై సూత్రాన్ని మళ్ళీ మూల్యాంకనం చేయడం మనకు లభిస్తుంది:

IB = Vi - 0.7 V / RB

= 10 V - 0.7 V / 150 kΩ = 62 μA,

IB = 62 μA నుండి > ICsat / cdc = 40 μA

ఇది మేము RB = 150 kΩ ను ఉపయోగించాల్సి ఉందని నిర్ధారిస్తుంది

స్విచ్చింగ్ ట్రాన్సిస్టర్లను లెక్కిస్తోంది

ఒక వోల్టేజ్ స్థాయి నుండి మరొక వోల్టేజ్ స్థాయికి వేగంగా మారడం వలన స్విచింగ్ ట్రాన్సిస్టర్లు అని పిలువబడే ప్రత్యేక ట్రాన్సిస్టర్లను మీరు కనుగొంటారు.

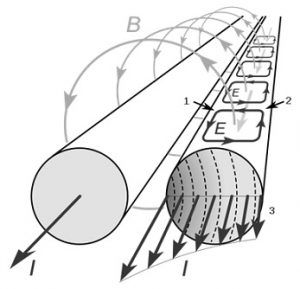

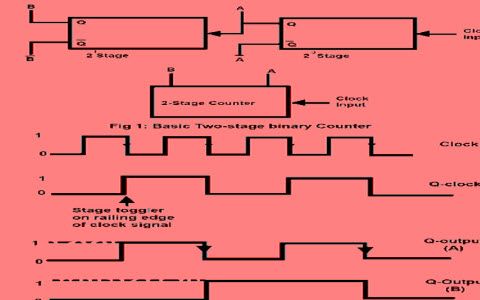

కింది మూర్తి ts, td, tr, మరియు tf గా సూచించబడిన సమయ వ్యవధులను పరికరం యొక్క కలెక్టర్ కరెంట్తో పోలుస్తుంది.

కలెక్టర్ వేగం ప్రతిస్పందనపై కాల వ్యవధుల ప్రభావం క్రింద చూపిన విధంగా కలెక్టర్ ప్రస్తుత ప్రతిస్పందన ద్వారా నిర్వచించబడుతుంది:

ట్రాన్సిస్టర్ “ఆఫ్” నుండి “ఆన్” స్థితికి మారడానికి అవసరమైన మొత్తం సమయం t (ఆన్) గా సూచించబడుతుంది మరియు సూత్రం ద్వారా దీన్ని స్థాపించవచ్చు:

t (ఆన్) = tr + td

ఇన్పుట్ స్విచ్చింగ్ సిగ్నల్ స్థితిని మారుస్తున్నప్పుడు మరియు ట్రాన్సిస్టర్ అవుట్పుట్ మార్పుకు ప్రతిస్పందిస్తున్నప్పుడు జరుగుతున్న ఆలస్యాన్ని ఇక్కడ td గుర్తిస్తుంది. సమయం tr తుది మార్పిడి ఆలస్యాన్ని 10% నుండి 90% వరకు సూచిస్తుంది.

ఆన్ చేయబడిన స్థితి నుండి ఆపివేయబడిన స్థితికి బిజెటి తీసుకున్న మొత్తం సమయం టి (ఆఫ్) గా సూచించబడుతుంది మరియు సూత్రం ద్వారా వ్యక్తీకరించబడుతుంది:

t (ఆఫ్) = ts + tf

ts నిల్వ సమయాన్ని నిర్ణయిస్తుంది, అయితే పతనం సమయాన్ని అసలు విలువలో 90% నుండి 10% వరకు tf గుర్తిస్తుంది.

పైన పేర్కొన్న గ్రాఫ్కు సూచించండి, సాధారణ ప్రయోజనం BJT కోసం, కలెక్టర్ ప్రస్తుత Ic = 10 mA అయితే, మేము దీనిని చూడవచ్చు:

ts = 120 ns, td = 25 ns, tr = 13 ns, tf = 12 ns

అంటే t (on) = tr + td = 13 ns + 25 ns = 38 ns

t (ఆఫ్) = ts + tf = 120 ns + 12 ns = 132 ns

మునుపటి: ఇంట్లో పిసిబి ఎలా తయారు చేయాలి తర్వాత: జెనర్ డయోడ్ సర్క్యూట్లు, లక్షణాలు, లెక్కలు