ఒక యుగం ఉంది, ఇక్కడ కంప్యూటర్లు చాలా మముత్ పరిమాణంలో ఉన్నాయి, వాటిని వ్యవస్థాపించడానికి, సులభంగా గది స్థలం అవసరం. కానీ ఈ రోజు అవి చాలా అభివృద్ధి చెందాయి, వాటిని మనం సులభంగా నోట్బుక్లుగా కూడా తీసుకెళ్లగలము. ఇంటిగ్రేటెడ్ సర్క్యూట్ల భావన దీనిని సాధ్యం చేసిన ఆవిష్కరణ. లో ఇంటిగ్రేటెడ్ సర్క్యూట్లు , పెద్ద సంఖ్యలో క్రియాశీల మరియు నిష్క్రియాత్మక అంశాలు క్రాస్ సెక్షన్లో 50 నుండి 50 మిల్లుల చిన్న సిలికాన్ పొరపై వాటి ఇంటర్ కనెక్షన్లతో పాటు అభివృద్ధి చేయబడతాయి. అటువంటి సర్క్యూట్ల ఉత్పత్తికి అనుసరించే ప్రాథమిక ప్రక్రియలలో ఎపిటాక్సియల్ పెరుగుదల, ముసుగు అపరిశుభ్రత వ్యాప్తి, ఆక్సైడ్ పెరుగుదల మరియు ఆక్సైడ్ ఎచింగ్ ఉన్నాయి, నమూనా తయారీకి ఫోటోలిథోగ్రఫీని ఉపయోగించడం.

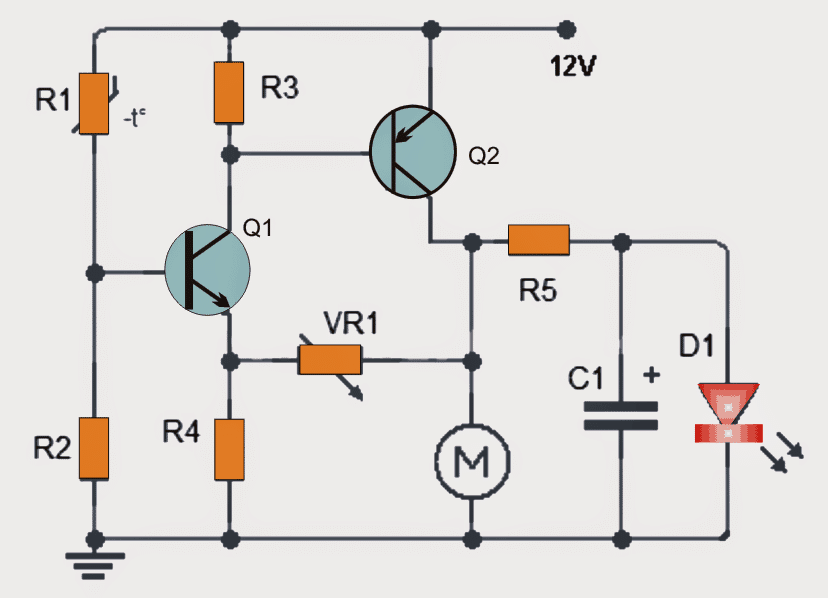

పొరపై ఉన్న భాగాలలో రెసిస్టర్లు, ట్రాన్సిస్టర్లు, డయోడ్లు, కెపాసిటర్లు మొదలైనవి ఉన్నాయి ... IC లలో ఉత్పత్తి చేయడానికి అత్యంత క్లిష్టమైన అంశం ట్రాన్సిస్టర్లు. ట్రాన్సిస్టర్లు వివిధ రకాలు CMOS, BJT, FET వంటివి. అవసరాల ఆధారంగా ఐసి ద్వారా అమలు చేయవలసిన ట్రాన్సిస్టర్ టెక్నాలజీ రకాన్ని మేము ఎంచుకుంటాము. ఈ వ్యాసంలో మనకు భావన గురించి తెలుసుకుందాం CMOS కల్పన (లేదా) ట్రాన్సిస్టర్లను CMOS గా కల్పించడం.

CMOS ఫ్యాబ్రికేషన్

తక్కువ విద్యుత్ వెదజల్లే అవసరం కోసం CMOS టెక్నాలజీ ట్రాన్సిస్టర్లను అమలు చేయడానికి ఉపయోగిస్తారు. మాకు వేగవంతమైన సర్క్యూట్ అవసరమైతే ట్రాన్సిస్టర్లు అమలు చేయబడతాయి IC ఉపయోగిస్తోంది బిజెటి . యొక్క ఫాబ్రికేషన్ CMOS ట్రాన్సిస్టర్లు IC లను మూడు వేర్వేరు పద్ధతులలో చేయవచ్చు.

N- బావి / P- బావి సాంకేతికత, ఇక్కడ n- రకం విస్తరణ p- రకం ఉపరితలంపై జరుగుతుంది లేదా p- రకం విస్తరణ వరుసగా n- రకం ఉపరితలంపై జరుగుతుంది.

ది ట్విన్ వెల్ టెక్నాలజీ , ఎక్కడ NMOS మరియు PMOS ట్రాన్సిస్టర్ ఒక ఉపరితలం కాకుండా, ఎపిటాక్సియల్ గ్రోత్ బేస్ మీద ఏకకాలంలో వ్యాపించడం ద్వారా పొరపై అభివృద్ధి చేయబడతాయి.

సిలికాన్ ఆన్ ఇన్సులేటర్ ప్రాసెస్, ఇక్కడ సిలికాన్ను సబ్స్ట్రేట్గా ఉపయోగించడం కంటే, ఇన్సులేటర్ పదార్థం వేగం మరియు గొళ్ళెం-అప్ ససెప్టబిలిటీని మెరుగుపరచడానికి ఉపయోగిస్తారు.

N- బాగా / P- బాగా టెక్నాలజీ

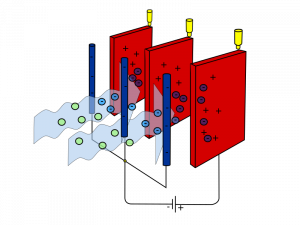

రెండింటినీ సమగ్రపరచడం ద్వారా CMOS పొందవచ్చు NMOS మరియు PMOS ట్రాన్సిస్టర్లు అదే సిలికాన్ పొర మీద. ఎన్-వెల్ టెక్నాలజీలో పి-టైప్ ఉపరితలంపై ఎన్-టైప్ బావి విస్తరించి ఉంటుంది, అయితే పి-బావిలో ఇది ఉప పద్యం.

CMOS ఫ్యాబ్రికేషన్ స్టెప్స్

ది CMOS కల్పన ప్రక్రియ ప్రవాహం N- బావి / పి-వెల్ టెక్నాలజీని ఉపయోగించి తయారుచేసేటప్పుడు ఇరవై ప్రాథమిక కల్పన దశలను ఉపయోగించి నిర్వహిస్తారు.

N ను ఉపయోగించి CMOS ను తయారు చేయడం

దశ 1: మొదట మేము కల్పన కోసం ఒక బేస్ గా ఒక ఉపరితలం ఎంచుకుంటాము. N- బాగా, P- రకం సిలికాన్ ఉపరితలం ఎంపిక చేయబడింది.

సబ్స్ట్రేట్

దశ 2 - ఆక్సీకరణ: N- రకం మలినాలను ఎంచుకున్న విస్తరణ SiO2 ను ఒక అవరోధంగా ఉపయోగించి సాధించవచ్చు, ఇది పొర యొక్క భాగాలను ఉపరితల కాలుష్యం నుండి రక్షిస్తుంది. SiOరెండుసుమారు 1000 వద్ద ఆక్సీకరణ గదిలో అధిక-నాణ్యత ఆక్సిజన్ మరియు హైడ్రోజన్కు ఉపరితలాన్ని బహిర్గతం చేసే ఆక్సీకరణ ప్రక్రియ ద్వారా నిర్దేశించబడుతుంది0సి

ఆక్సీకరణ

దశ 3 - ఫోటోరేసిస్ట్ యొక్క పెరుగుదల: సెలెక్టివ్ ఎచింగ్ను అనుమతించడానికి ఈ దశలో, SiO2 పొర ఫోటోలిథోగ్రఫీ ప్రక్రియకు లోబడి ఉంటుంది. ఈ ప్రక్రియలో, పొర ఫోటోసెన్సిటివ్ ఎమల్షన్ యొక్క ఏకరీతి చిత్రంతో పూత పూయబడుతుంది.

ఫోటోరేసిస్ట్ యొక్క పెరుగుదల

దశ 4 - మాస్కింగ్: ఈ దశ ఫోటోలిథోగ్రఫీ ప్రక్రియ యొక్క కొనసాగింపు. ఈ దశలో, స్టెన్సిల్ ఉపయోగించి బహిరంగత యొక్క కావలసిన నమూనా తయారు చేయబడుతుంది. ఈ స్టెన్సిల్ను ఫోటోరేసిస్ట్పై ముసుగుగా ఉపయోగిస్తారు. ఉపరితలం ఇప్పుడు బహిర్గతమైంది UV కిరణాలు ముసుగు యొక్క బహిర్గత ప్రాంతాల క్రింద ఉన్న ఫోటోరేసిస్ట్ పాలిమరైజ్ అవుతుంది.

ఫోటోరేసిస్ట్ యొక్క మాస్కింగ్

దశ 5 - బహిర్గతం చేయని ఫోటోరేసిస్ట్ యొక్క తొలగింపు: ముసుగు తొలగించబడుతుంది మరియు ట్రైక్లోరెథైలీన్ వంటి రసాయనాన్ని ఉపయోగించి పొరను అభివృద్ధి చేయడం ద్వారా ఫోటోరేసిస్ట్ యొక్క బహిర్గతం చేయని ప్రాంతం కరిగిపోతుంది.

ఫోటోరేసిస్ట్ యొక్క తొలగింపు

దశ 6 - చెక్కడం: పొరను హైడ్రోఫ్లోరిక్ ఆమ్లం యొక్క ఎచింగ్ ద్రావణంలో నిమజ్జనం చేస్తారు, ఇది డోపాంట్లు వ్యాప్తి చెందవలసిన ప్రాంతాల నుండి ఆక్సైడ్ను తొలగిస్తుంది.

SiO2 యొక్క చెక్కడం

దశ 7 - మొత్తం ఫోటోరేసిస్ట్ పొరను తొలగించడం: అది జరుగుతుండగా చెక్కడం ప్రక్రియ , ఫోటోరేసిస్ట్ పొర ద్వారా రక్షించబడిన SiO2 యొక్క భాగాలు ప్రభావితం కావు. ఫోటోరేసిస్ట్ ముసుగు ఇప్పుడు రసాయన ద్రావకం (వేడి H2SO4) తో తొలగించబడింది.

ఫోటోరేసిస్ట్ లేయర్ యొక్క తొలగింపు

దశ 8 - N- బావి నిర్మాణం: N- రకం మలినాలను బహిర్గతం చేసిన ప్రాంతం ద్వారా p- రకం ఉపరితలంలోకి విస్తరిస్తారు, తద్వారా N- బావి ఏర్పడుతుంది.

N- బావి నిర్మాణం

దశ 9 - SiO2 యొక్క తొలగింపు: SiO2 యొక్క పొర ఇప్పుడు హైడ్రోఫ్లోరిక్ ఆమ్లాన్ని ఉపయోగించి తొలగించబడుతుంది.

SiO2 యొక్క తొలగింపు

దశ 10 - పాలిసిలికాన్ నిక్షేపణ: గేట్ యొక్క తప్పుగా అమర్చడం a CMOS ట్రాన్సిస్టర్ సర్క్యూట్కు హాని కలిగించే అవాంఛిత కెపాసిటెన్స్కు దారితీస్తుంది. కాబట్టి ఈ 'స్వీయ-సమలేఖన గేట్ ప్రక్రియ' ను నివారించడానికి, అయాన్ ఇంప్లాంటేషన్ ఉపయోగించి మూలం మరియు కాలువ ఏర్పడటానికి ముందు గేట్ ప్రాంతాలు ఏర్పడతాయి.

పాలిసిలికాన్ నిక్షేపణ

గేట్ ఏర్పడటానికి పాలిసిలికాన్ ఉపయోగించబడుతుంది ఎందుకంటే ఇది 8000 కన్నా ఎక్కువ ఉష్ణోగ్రతను తట్టుకోగలదు0సి మరియు మూలం మరియు కాలువ ఏర్పడటానికి ఒక పొరను ఎనియలింగ్ పద్ధతులకు గురిచేసినప్పుడు. పాలిసిలికాన్ ఉపయోగించడం ద్వారా జమ చేయబడుతుంది రసాయన నిక్షేపణ ప్రక్రియ గేట్ ఆక్సైడ్ యొక్క పలుచని పొరపై. పాలిసిలికాన్ పొర కింద ఉన్న ఈ సన్నని గేట్ ఆక్సైడ్ గేట్ ప్రాంతం కింద మరింత డోపింగ్ నిరోధిస్తుంది.

దశ 11 - గేట్ ప్రాంతం ఏర్పాటు: గేట్ ఏర్పాటుకు అవసరమైన రెండు ప్రాంతాలు తప్ప NMOS మరియు PMOS ట్రాన్సిస్టర్లు పాలిసిలికాన్ యొక్క మిగిలిన భాగం తీసివేయబడుతుంది.

గేట్ ప్రాంతం ఏర్పాటు

దశ 12 - ఆక్సీకరణ ప్రక్రియ: ఒక ఆక్సీకరణ పొర పొరపై జమ చేయబడుతుంది, ఇది మరింత కవచంగా పనిచేస్తుంది విస్తరణ మరియు మెటలైజేషన్ ప్రక్రియలు .

ఆక్సీకరణ ప్రక్రియ

దశ 13 - మాస్కింగ్ మరియు విస్తరణ: మాస్కింగ్ ప్రక్రియను ఉపయోగించి n- రకం మలినాలను వ్యాప్తి చేయడానికి ప్రాంతాలను తయారు చేయడానికి చిన్న ఖాళీలు తయారు చేయబడతాయి.

మాస్కింగ్

విస్తరణ ప్రక్రియను ఉపయోగించి NMOS యొక్క టెర్మినల్స్ ఏర్పడటానికి మూడు n + ప్రాంతాలు అభివృద్ధి చేయబడతాయి.

ఎన్-డిఫ్యూజన్

దశ 14 - ఆక్సైడ్ తొలగింపు: ఆక్సైడ్ పొర తీసివేయబడుతుంది.

ఆక్సైడ్ తొలగింపు

దశ 15 - పి-రకం విస్తరణ: PMOS p- రకం విస్తరణ యొక్క టెర్మినల్స్ ఏర్పడటానికి n- రకం విస్తరణ మాదిరిగానే జరుగుతుంది.

పి-టైప్ డిఫ్యూజన్

దశ 16 - చిక్కటి ఫీల్డ్ ఆక్సైడ్ వేయడం: మెటల్ టెర్మినల్స్ ఏర్పడటానికి ముందు, మందపాటి ఫీల్డ్ ఆక్సైడ్ టెర్మినల్స్ అవసరం లేని పొర యొక్క ప్రాంతాలకు రక్షణ పొరను ఏర్పరుస్తుంది.

చిక్కటి ఫీల్డ్ ఆక్సైడ్ లేయర్

దశ 17 - మెటలైజేషన్: ఈ దశ మెటల్ టెర్మినల్స్ ఏర్పడటానికి ఉపయోగించబడుతుంది, ఇది ఇంటర్ కనెక్షన్లను అందిస్తుంది. అల్యూమినియం మొత్తం పొరపై వ్యాపించింది.

మెటలైజేషన్

దశ 18 - అదనపు లోహాన్ని తొలగించడం: అదనపు లోహం పొర నుండి తొలగించబడుతుంది.

దశ 19 - టెర్మినల్స్ ఏర్పాటు: అదనపు లోహ టెర్మినల్స్ తొలగించిన తరువాత ఏర్పడిన ఖాళీలలో ఇంటర్ కనెక్షన్ల కోసం ఏర్పడతాయి.

టెర్మినల్స్ ఏర్పాటు

దశ 20 - టెర్మినల్ పేర్లను కేటాయించడం: యొక్క టెర్మినల్స్కు పేర్లు కేటాయించబడతాయి NMOS మరియు PMOS ట్రాన్సిస్టర్లు .

టెర్మినల్ పేర్లను కేటాయించడం

పి వెల్ టెక్నాలజీని ఉపయోగించి CMOS ను తయారు చేయడం

P- బావి ప్రక్రియ N బావి ప్రక్రియను పోలి ఉంటుంది, ఇక్కడ n- రకం ఉపరితలం ఉపయోగించబడుతుంది మరియు p- రకం వ్యాప్తి చెందుతుంది. సాధారణంగా సరళత కోసం, N బాగా ప్రక్రియకు ప్రాధాన్యత ఇవ్వబడుతుంది.

CMOS యొక్క ట్విన్ ట్యూబ్ ఫ్యాబ్రికేషన్

ట్విన్-ట్యూబ్ ప్రాసెస్ను ఉపయోగించడం ద్వారా పి మరియు ఎన్-టైప్ పరికరాల లాభాలను నియంత్రించవచ్చు. వివిధ దశలు ఉన్నాయి CMOS యొక్క కల్పన ట్విన్-ట్యూబ్ పద్ధతిని ఉపయోగించడం ఈ క్రింది విధంగా ఉన్నాయి

- తేలికగా డోప్ చేయబడిన n లేదా పి-రకం ఉపరితలం తీసుకోబడుతుంది మరియు ఎపిటాక్సియల్ పొర ఉపయోగించబడుతుంది. ఎపిటాక్సియల్ పొర చిప్లోని గొళ్ళెం సమస్యను రక్షిస్తుంది.

- కొలిచిన మందం మరియు ఖచ్చితమైన డోపాంట్ ఏకాగ్రత కలిగిన అధిక స్వచ్ఛత సిలికాన్ పొరలను పెంచుతారు.

- P మరియు N లకు బాగా గొట్టాల నిర్మాణం.

- విస్తరణ ప్రక్రియల సమయంలో కాలుష్యం నుండి రక్షణ కోసం సన్నని ఆక్సైడ్ నిర్మాణం.

- అయాన్ ఇంప్లాంటేషన్ పద్ధతులను ఉపయోగించి మూలం మరియు కాలువ ఏర్పడతాయి.

- లోహ పరిచయాల కోసం భాగాలను తయారు చేయడానికి కోతలు తయారు చేస్తారు.

- మెటల్ పరిచయాలను గీయడానికి మెటలైజేషన్ జరుగుతుంది

CMOS IC లేఅవుట్

యొక్క ఎగువ వీక్షణ CMOS కు కల్పన మరియు లేఅవుట్ ఇవ్వబడింది. ఇక్కడ వివిధ లోహ పరిచయాలు మరియు N బాగా వ్యాప్తి చెందడం స్పష్టంగా చూడవచ్చు.

CMOS IC లేఅవుట్

అందువలన, ఇది అన్ని గురించి CMOS కల్పన పద్ధతులు . 1-ఇన్-స్క్వేర్ పొరను 400 చిప్స్ ఉపరితల వైశాల్యం 50 మిల్లు 50 మిల్స్ ద్వారా విభజించాము. ట్రాన్సిస్టర్ను రూపొందించడానికి 50 మిల్ 2 విస్తీర్ణం పడుతుంది. అందువల్ల ప్రతి ఐసిలో 2 ట్రాన్సిస్టర్లు ఉంటాయి, అందువల్ల ప్రతి పొరపై 2 x 400 = 800 ట్రాన్సిస్టర్లు నిర్మించబడతాయి. ప్రతి బ్యాచ్లో 10 పొరలు ప్రాసెస్ చేయబడితే 8000 ట్రాన్సిస్టర్లను ఒకేసారి తయారు చేయవచ్చు. IC లో మీరు గమనించిన వివిధ భాగాలు ఏమిటి?