సాధారణంగా, పూర్తి వ్యవకలనం ఎక్కువగా ఉపయోగించబడుతుంది మరియు అవసరమైన కాంబినేషన్ లాజిక్ సర్క్యూట్లు . ఇది ఒక ప్రాథమిక ఎలక్ట్రానిక్ పరికరం, ఇది రెండు బైనరీ సంఖ్యల వ్యవకలనం చేయడానికి ఉపయోగిస్తారు. మునుపటి వ్యాసంలో, ఇప్పటికే మేము ప్రాథమిక సిద్ధాంతాన్ని ఇచ్చాము సగం యాడర్ & పూర్తి యాడర్ ఇది గణన కోసం బైనరీ అంకెలను ఉపయోగిస్తుంది. అదేవిధంగా, పూర్తి-వ్యవకలనం వ్యవకలనం కోసం 0,1 వంటి బైనరీ అంకెలను ఉపయోగిస్తుంది. దీని సర్క్యూట్ను OR, Ex-OR, NAND గేట్ వంటి లాజిక్ గేట్లతో నిర్మించవచ్చు. ఈ వ్యవకలనం యొక్క ఇన్పుట్లు A, B, బిన్ మరియు అవుట్పుట్లు D, Bout.

ఈ వ్యాసం పూర్తి-వ్యవకలన సిద్ధాంత ఆలోచనను ఇస్తుంది, ఇందులో సబ్ట్రాక్టర్ అంటే ఏమిటి, లాజిక్ గేట్లతో డిజైన్, ట్రూత్ టేబుల్ మొదలైనవి ఉంటాయి. హెచ్డిఎల్ ప్రాక్టికల్ ల్యాబ్లో ఈ అంశాల ద్వారా వెళ్ళగలిగే ఇంజనీరింగ్ విద్యార్థులకు ఈ వ్యాసం ఉపయోగపడుతుంది.

వ్యవకలనం అంటే ఏమిటి?

బైనరీ అంకెలు వ్యవకలనం వ్యవకలన సర్క్యూట్ సహాయంతో చేయవచ్చు. ఇది ఒక రకమైన కాంబినేషన్ లాజిక్ సర్క్యూట్, ఇది 0s మరియు 1s వంటి రెండు బైనరీ అంకెలను వ్యవకలనం చేయడానికి ఉపయోగిస్తారు. బైనరీ అంకెలను 0 నుండి 0 లేదా 0 నుండి 1 వరకు తీసివేయడం ఫలితాన్ని మార్చదు, 1 నుండి 1 వరకు వ్యవకలనం 0 గా ఉంటుంది, అయితే 1 నుండి 0 వరకు వ్యవకలనం తీసుకోవాలి.

ఉదాహరణకు, రెండు-బిట్ సబ్ట్రాక్టర్ సర్క్యూట్లో A & B వంటి రెండు ఇన్పుట్లు ఉంటాయి, అయితే అవుట్పుట్లు తేడా మరియు రుణం తీసుకుంటాయి. ఈ సర్క్యూట్ ప్రతి డేటా ఇన్పుట్లలో ఉన్న ఇన్వర్టర్లతో పాటు యాడర్స్ తో నిర్మించబడవచ్చు మరియు FA యొక్క మునుపటి దశ యొక్క borrow ణం (బిన్) ఇన్పుట్.

సబ్ట్రాక్టర్లను సగం సబ్ట్రాక్టర్ మరియు ఫుల్ సబ్ట్రాక్టర్ వంటి రెండు రకాలుగా వర్గీకరించారు. ఇక్కడ మేము పూర్తి వ్యవకలనం గురించి చర్చిస్తున్నాము.

పూర్తి వ్యవకలనం అంటే ఏమిటి?

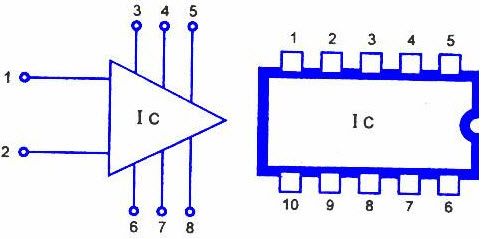

ఇది ఎలక్ట్రానిక్ పరికరం లేదా లాజిక్ సర్క్యూట్ ఇది రెండు బైనరీ అంకెలను వ్యవకలనం చేస్తుంది. ఇది డిజిటల్ ఎలక్ట్రానిక్స్లో ఉపయోగించే కాంబినేషన్ లాజిక్ సర్క్యూట్. అనేక కాంబినేషన్ సర్క్యూట్లు అందుబాటులో ఉన్నాయి ఇంటిగ్రేటెడ్ సర్క్యూట్ టెక్నాలజీ అవి యాడర్లు, ఎన్కోడర్లు, డీకోడర్లు మరియు మల్టీప్లెక్సర్లు. ఈ వ్యాసంలో, మేము సగం నిర్మాణం మరియు సత్య పట్టిక వంటి పదాలను ఉపయోగించి దాని నిర్మాణం గురించి చర్చించబోతున్నాము.

పూర్తి వ్యవకలనం

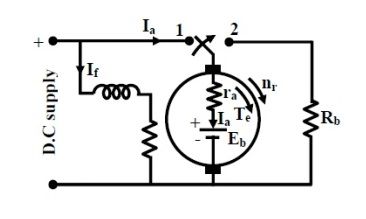

దీని రూపకల్పన రెండు సగం సబ్ట్రాక్టర్ల ద్వారా చేయవచ్చు, ఇందులో మినియెండ్, సబ్ట్రాహెండ్ మరియు రుణం వంటి మూడు ఇన్పుట్లు ఉంటాయి, ఇన్పుట్లలో బిట్ borrow ణం రెండు బైనరీ అంకెలు వ్యవకలనం నుండి పొందబడుతుంది మరియు తదుపరి అధిక-ఆర్డర్ జత నుండి తీసివేయబడుతుంది. బిట్స్, అవుట్పుట్లు తేడా మరియు రుణం.

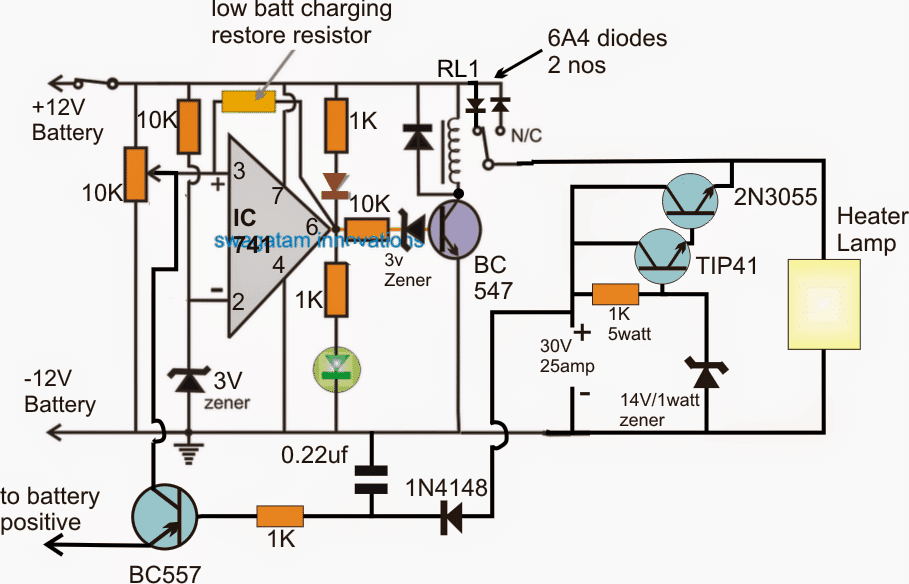

ది పూర్తి వ్యవకలన బ్లాక్ రేఖాచిత్రం క్రింద చూపబడింది. సగం వ్యవకలనం యొక్క మొట్టమొదటి ప్రతికూలత ఏమిటంటే, ఈ వ్యవకలనంలో మేము బారో బిట్ చేయలేము. దాని రూపకల్పనలో, వాస్తవానికి మనం సర్క్యూట్లో బారో బిట్ చేయవచ్చు మరియు మిగిలిన రెండు i / ps లతో తీసివేయవచ్చు. ఇక్కడ A మినియెండ్, B అనేది సబ్ట్రాహెండ్ & బిన్ అప్పుగా ఉంది. అవుట్పుట్లు తేడా (తేడా) & బౌట్ (బారో అవుట్). అదనపు సబ్ట్రాక్టర్ సర్క్యూట్ అదనపు OR గేట్తో రెండు సగం సబ్ట్రాక్టర్లను ఉపయోగించడం ద్వారా పొందవచ్చు.

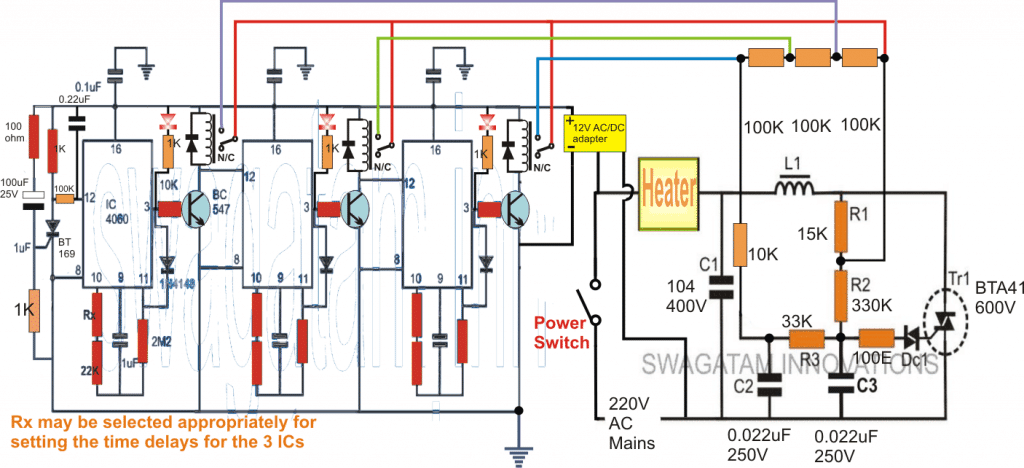

లాజిక్ గేట్లతో పూర్తి సబ్ట్రాక్టర్ సర్క్యూట్ రేఖాచిత్రం

ది ప్రాథమిక గేట్ ఉపయోగించి పూర్తి వ్యవకలనం యొక్క సర్క్యూట్ రేఖాచిత్రం s క్రింది బ్లాక్ రేఖాచిత్రంలో చూపబడింది. ఈ సర్క్యూట్ రెండు సగం-వ్యవకలన సర్క్యూట్లతో చేయవచ్చు.

ప్రారంభ సగం-వ్యవకలన సర్క్యూట్లో, బైనరీ ఇన్పుట్లు A మరియు B. మునుపటి సగం-వ్యవకలన వ్యాసంలో మనం చర్చించినట్లుగా, ఇది తేడా (తేడా) & రుణాలు అనే రెండు ఉత్పాదనలను ఉత్పత్తి చేస్తుంది.

లాజిక్ గేట్లను ఉపయోగించి పూర్తి వ్యవకలనం

ఎడమ సబ్ట్రాక్టర్ యొక్క o / p వ్యత్యాసం ఎడమ సగం-వ్యవకలన సర్క్యూట్కు ఇవ్వబడుతుంది. కుడి సగం సబ్ట్రాక్టర్ సర్క్యూట్ యొక్క ఇన్పుట్కు తేడా అవుట్పుట్ మరింత అందించబడుతుంది. మేము తరువాతి యొక్క ఇతర i / p అంతటా బిరోను బిట్లో అందించాము సగం వ్యవకలన సర్క్యూట్ . మరోసారి అది డిఫ్ అవుట్ ను ఇస్తుంది అలాగే బిట్ అవుట్ ను కూడా ఇస్తుంది. ఈ వ్యవకలనం యొక్క తుది అవుట్పుట్ తేడా-అవుట్పుట్.

మరోవైపు, సగం సబ్ట్రాక్టర్ సర్క్యూట్లలోని బారో అవుట్ లేదా లాజిక్ గేట్కు అనుసంధానించబడి ఉంది. సబ్ట్రాక్టర్ యొక్క రెండు అవుట్పుట్ బిట్ల కోసం OR లాజిక్ ఇవ్వడం కంటే, మేము సబ్ట్రాక్టర్ నుండి తుది బారోను పొందుతాము. MSB ను సూచించడానికి చివరి బారో అవుట్ (చాలా ముఖ్యమైన బిట్).

దీని యొక్క అంతర్గత సర్క్యూట్ను మనం గమనిస్తే, NAND గేట్తో రెండు హాఫ్ సబ్ట్రాక్టర్లను మరియు అదనపు OR గేట్తో XOR గేట్ను చూడవచ్చు.

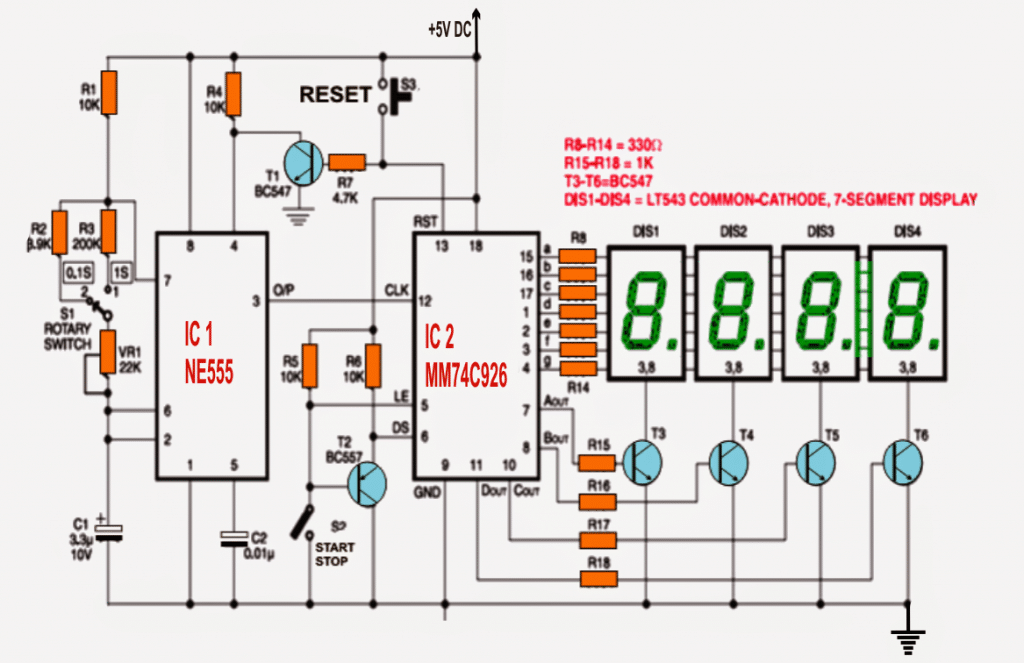

పూర్తి వ్యవకలన సత్య పట్టిక

ఇది వ్యవకలన సర్క్యూట్ రెండు బిట్ల మధ్య వ్యవకలనాన్ని అమలు చేస్తుంది, దీనిలో 3- ఇన్పుట్లు (A, B, మరియు బిన్) మరియు రెండు అవుట్పుట్లు (D మరియు Bout) ఉన్నాయి. ఇక్కడ ఇన్పుట్లు మినియుండ్, సబ్ట్రాహెండ్ మరియు మునుపటి రుణాలను సూచిస్తాయి, అయితే రెండు అవుట్పుట్లను రుణాలు o / p మరియు తేడాగా సూచిస్తారు. కింది చిత్రం పూర్తి-వ్యవకలనం యొక్క సత్య పట్టికను చూపుతుంది.

ఇన్పుట్లు | అవుట్పుట్లు | |||

మినియుండ్ (ఎ) | సబ్ట్రాహెండ్ (బి) | రుణం (బిన్) | తేడా (డి) | రుణం (బౌట్) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

కె-మ్యాప్

యొక్క సరళీకరణ పూర్తి వ్యవకలనం K- మ్యాప్ పై వ్యత్యాసం మరియు రుణం క్రింద చూపబడింది.

వ్యత్యాసం మరియు బిన్ యొక్క సమీకరణాలు క్రింద పేర్కొనబడ్డాయి.

వ్యత్యాసం యొక్క వ్యక్తీకరణ,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

బారో యొక్క వ్యక్తీకరణ,

Bout = A’Bin + A’B + BBin

పూర్తి వ్యవకలన సర్క్యూట్ యొక్క క్యాస్కేడింగ్

ఇంతకుముందు, నిర్మాణం, లాజిక్ గేట్లతో సర్క్యూట్ రేఖాచిత్రం వంటి అవలోకనాన్ని మేము చర్చించాము. మేము రెండు ఇతర 1-బిట్ సంఖ్యలను తీసివేయాలనుకుంటే, ఈ వ్యవకలన సర్క్యూట్ సింగిల్ బిట్ సంఖ్యలను క్యాస్కేడ్ చేయడానికి చాలా సహాయపడుతుంది మరియు రెండు బైనరీ సంఖ్యల కంటే ఎక్కువ తీసివేస్తుంది. ఇటువంటి సందర్భాల్లో, NOT లాజిక్ గేట్ సహాయంతో పూర్తి యాడర్ క్యాస్కేడ్ సర్క్యూట్ ఉపయోగించబడుతుంది. 2 యొక్క పూరక సాంకేతికతను ఉపయోగించి సర్క్యూట్ను పూర్తి యాడెర్ నుండి పూర్తి సబ్ట్రాక్టర్గా మార్చవచ్చు.

సాధారణంగా, పూర్తి గేటు కోసం సబ్ట్రాహెండ్ ఇన్పుట్లను NOT గేట్ ఉపయోగించి విలోమం చేయండి. ఈ మినియుండ్ (నాన్ఇన్వర్టెడ్ ఇన్పుట్) & సబ్ట్రాహెండ్ (విలోమ ఇన్పుట్) ను జోడించడం ద్వారా, ఎఫ్ఎ సర్క్యూట్ యొక్క ఎల్ఎస్బి (క్యారీ ఇన్పుట్) 1, అంటే లాజిక్ హై అంటే 2 యొక్క కాంప్లిమెంట్ టెక్నిక్ ఉపయోగించి రెండు బైనరీ అంకెలను తీసివేస్తాము. FA యొక్క అవుట్పుట్ డిఫ్ బిట్ & మేము క్యారీ అవుట్ ను విలోమం చేస్తే అప్పుడు మేము MSB ను పొందవచ్చు, లేకపోతే బారో బిట్. అసలైన, మేము సర్క్యూట్ను రూపొందించవచ్చు, తద్వారా అవుట్పుట్ గమనించవచ్చు.

వెరిలోగ్ కోడ్

కోడింగ్ భాగం కోసం, మొదట, లాజిక్ సర్క్యూట్ రేఖాచిత్రం యొక్క మోడలింగ్ యొక్క నిర్మాణ మార్గాన్ని మనం తనిఖీ చేయాలి. దీని యొక్క లాజిక్ రేఖాచిత్రాన్ని AND గేట్, సగం సబ్ట్రాక్టర్ సర్క్యూట్లు మరియు AND, OR, NOT, XOR గేట్లు వంటి లాజిక్ గేట్ల కలయికను ఉపయోగించి నిర్మించవచ్చు. స్ట్రక్చరల్ మోడలింగ్ మాదిరిగా, ప్రతి ప్రాథమిక ఎలిమెంటల్ అమరిక కోసం మేము వివిధ మాడ్యూళ్ళను వివరిస్తాము. కింది కోడ్లో, ప్రతి గేట్కు వేర్వేరు మాడ్యూళ్ళను నిర్వచించవచ్చు.

ఈ మాడ్యూల్ OR గేట్ కోసం.

ఇన్పుట్: a0, b0

అవుట్పుట్: c0

చివరగా, మేము ఈ గేట్ ఖచ్చితమైన మాడ్యూళ్ళను ఒకే మాడ్యూల్గా ఏకం చేస్తాము. దాని కోసం, ఇక్కడ మేము మాడ్యూల్ యొక్క ఇన్స్టాంటియేషన్ను ఉపయోగించుకుంటాము. విభిన్న ఇన్పుట్ సెట్ల కోసం ఖచ్చితమైన మాడ్యూల్ లేదా ఫంక్షన్ను ప్రతిబింబించాలనుకుంటే ఇప్పుడు ఈ ఇన్స్టాంటియేషన్ ఉపయోగించబడుతుంది. మొదట, మేము సగం వ్యవకలనాన్ని రూపకల్పన చేస్తాము, అప్పుడు ఈ మాడ్యూల్ పూర్తి వ్యవకలనాన్ని అమలు చేయడానికి ఉపయోగించబడుతుంది. దీన్ని అమలు చేయడానికి, మేము బౌట్ యొక్క వేరియబుల్ కోసం o / ps ను కలపడానికి OR గేట్ను ఉపయోగిస్తాము. ది పూర్తి వ్యవకలనం కోసం వెరిలోగ్ కోడ్ క్రింద చూపబడింది

మాడ్యూల్ or_gate (a0, b0, c0)

ఇన్పుట్ a0, b0

అవుట్పుట్ c0

c0 = a0 | ని కేటాయించండి b0

ఎండ్మోడ్యూల్

మాడ్యూల్ xor_gate (a1, b1, c1)

ఇన్పుట్ a1, b1

అవుట్పుట్ సి 1

c1 = a1 ^ b1 ని కేటాయించండి

ఎండ్మోడ్యూల్

మాడ్యూల్ మరియు_గేట్ (a2, b2, c2)

ఇన్పుట్ a2, b2

అవుట్పుట్ సి 2

c2 = a2 & b2 ని కేటాయించండి

ఎండ్మోడ్యూల్

మాడ్యూల్ నోట్గేట్ (a3, b3)

ఇన్పుట్ a3

అవుట్పుట్ బి 3

కేటాయించండి b3 = ~ a3

ఎండ్మోడ్యూల్

మాడ్యూల్ సగం_సబ్ట్రాక్టర్ (a4, b4, c4, d4)

ఇన్పుట్ a4, b4

అవుట్పుట్ సి 4, డి 4

వైర్ x

xor_gate u1 (a4, b4, c4)

మరియు_గేట్ u2 (x, b4, d4)

not_gate u3 (a4, x)

ఎండ్మోడ్యూల్

మాడ్యూల్ పూర్తి_సబ్ట్రాక్టర్ (A, B, బిన్, D, బౌట్)

ఇన్పుట్ A, B, బిన్

అవుట్పుట్ D, బౌట్

వైర్ p, q, r

సగం_సబ్ట్రాక్టర్ u4 (A, B, p, q)

సగం_సబ్ట్రాక్టర్ u5 (p, బిన్, D, r)

or_gate u6 (q, r, Bout)

ఎండ్మోడ్యూల్

4X1 మల్టీప్లెక్సర్ ఉపయోగించి పూర్తి సబ్ట్రాక్టర్

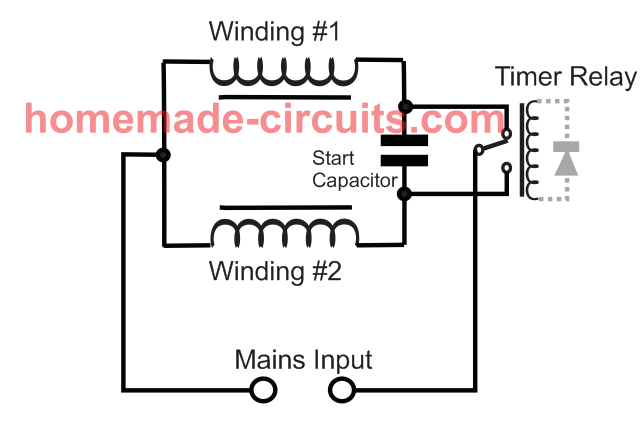

వ్యవకలనం యొక్క అమలు రెండు యొక్క పూరక పద్ధతి ద్వారా చేయవచ్చు. ఈ విధంగా మనకు 1-బిట్ విలోమం చేయడానికి మరియు ఒకదాన్ని క్యారీ బిట్లో చేర్చడానికి ఉపయోగించే 1-XOR గేట్ను ఉపయోగించడం అవసరం. DIFFERENCE యొక్క అవుట్పుట్ పూర్తి యాడర్ సర్క్యూట్లో అవుట్పుట్ SUM కు సమానంగా ఉంటుంది, అయితే BARROW o / p పూర్తి యాడర్ యొక్క క్యారీ అవుట్పుట్కు సమానంగా లేదు, అయితే ఇది విలోమంగా ఉంటుంది మరియు A - B = A + (-B) వంటి పొగడ్తలతో ఉంటుంది. = A + రెండు యొక్క బి.

4X1 మల్టీప్లెక్సర్ ఉపయోగించి దీని రూపకల్పన క్రింది లాజిక్ రేఖాచిత్రంలో చూపబడింది. కింది దశలను ఉపయోగించి ఈ డిజైన్ చేయవచ్చు.

4 ఎక్స్ 1 మల్టీప్లెక్సర్

- స్టెప్ 1 లో, సబ్ మరియు బారో వంటి రెండు అవుట్పుట్లు ఉన్నాయి. కాబట్టి మనం 2 మల్టీప్లెక్సర్లను ఎన్నుకోవాలి.

- దశ 2 లో, K- మ్యాప్లతో పాటు సత్య పట్టికను అమలు చేయవచ్చు

- దశ 3 లో, రెండు వేరియబుల్స్ మీ ఎంచుకున్న పంక్తిగా ఎంచుకోవచ్చు. ఉదాహరణకు, B & C ఈ సందర్భంలో ఉన్నాయి.

ట్రూత్ టేబుల్

ది పూర్తి వ్యవకలనం యొక్క సత్య పట్టిక 4X1 మల్టీప్లెక్సర్ను ఉపయోగించే సర్క్యూట్ కింది వాటిని కలిగి ఉంటుంది

TO | బి | సి | ఉప | రుణం |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

డీకోడర్ ఉపయోగించి పూర్తి వ్యవకలనం

3-8 డీకోడర్లను ఉపయోగించి పూర్తి సబ్ట్రాక్టర్ రూపకల్పన చురుకైన తక్కువ అవుట్పుట్లను ఉపయోగించి చేయవచ్చు. కింది లాజిక్ రేఖాచిత్రాన్ని ఉపయోగించి డీకోడర్ పనితీరును అనుకుందాం. డీకోడర్ 3-8 డీకోడర్లలో మూడు ఇన్పుట్లను కలిగి ఉంటుంది. సత్య పట్టిక ఆధారంగా, వ్యత్యాసం & రుణం యొక్క ఫలితాల కోసం మేము మినిటర్మ్స్ వ్రాయవచ్చు.

పై సత్య పట్టిక నుండి,

సత్య పట్టికలోని విభిన్న విధుల కోసం, మైనర్లను 1,2,4,7 గా వ్రాయవచ్చు మరియు అదేవిధంగా, రుణం కోసం, మైనర్లను 1,2,3,7 గా వ్రాయవచ్చు. 3-8 డీకోడర్లలో మూడు ఇన్పుట్లు అలాగే 8 అవుట్పుట్లు lik0 నుండి 7 సంఖ్యలు ఉంటాయి.

3-నుండి -8 డీకోడర్

సబ్ట్రాక్టర్ యొక్క ఇన్పుట్ 000 అయితే, అవుట్పుట్ ‘0’ యాక్టివ్గా ఉంటుంది మరియు ఇన్పుట్ 001 అయితే, అవుట్పుట్ ‘1’ యాక్టివ్గా ఉంటుంది.

ఇప్పుడు సబ్ట్రాక్టర్ యొక్క అవుట్పుట్లను 1, 2, 4 & 7 నుండి NAND గేట్కు అనుసంధానించవచ్చు, అప్పుడు అవుట్పుట్ తేడా ఉంటుంది. ఈ అవుట్పుట్లను ఇతర NAND లాజిక్ గేట్స్తో అనుసంధానించవచ్చు, ఇక్కడ అవుట్పుట్ రుణానికి మారుతుంది.

ఉదాహరణకు, ఇన్పుట్ 001 అయితే, అవుట్పుట్ 1 అవుతుంది అంటే అది సక్రియంగా ఉంటుంది. కాబట్టి అవుట్పుట్ చురుకుగా తక్కువగా ఉంటుంది మరియు అవుట్పుట్ ను NAND గేట్ నుండి డిఫరెన్స్ ఫంక్షన్ అని పిలుస్తారు మరియు హై మరియు borrow ణం ఫంక్షన్ కూడా అధికంగా మారుతుంది. అందువల్ల మనకు ఇష్టపడే అవుట్పుట్ లభిస్తుంది. చివరకు, డీకోడర్ పూర్తి వ్యవకలనం వలె పనిచేస్తుంది.

ప్రయోజనాలు మరియు అప్రయోజనాలు

ది వ్యవకలనం యొక్క ప్రయోజనాలు కింది వాటిని చేర్చండి.

- వ్యవకలనం యొక్క రూపకల్పన చాలా సులభం మరియు అమలు చేస్తుంది

- DSP లో శక్తి తగ్గింపు (డిజిటల్ సిగ్నల్ ప్రాసెసింగ్)

- గణన పనులను అధిక వేగంతో చేయవచ్చు.

ది వ్యవకలనం యొక్క ప్రతికూలతలు కింది వాటిని చేర్చండి.

- సగం వ్యవకలనంలో, మునుపటి దశ నుండి బారో లాంటి ఇన్పుట్ను అంగీకరించే పరిస్థితి లేదు.

- సర్క్యూట్ ఆలస్యం ద్వారా వ్యవకలన వేగం పాక్షికంగా ఉంటుంది.

అప్లికేషన్స్

వాటిలో కొన్ని పూర్తి-వ్యవకలనం యొక్క అనువర్తనాలు కింది వాటిని చేర్చండి

- సర్క్యూట్ ఇబ్బందిని తగ్గించడానికి గ్రాఫిక్స్ యొక్క అనువర్తనాల కోసం వీటిని సాధారణంగా కంప్యూటర్లలో ALU (అంకగణిత లాజిక్ యూనిట్) కొరకు CPU & GPU గా తీసివేయడానికి ఉపయోగిస్తారు.

- ఎలక్ట్రానిక్ కాలిక్యులేటర్లలో మరియు డిజిటల్ పరికరాల్లో వ్యవకలనం వంటి అంకగణిత విధులను నిర్వహించడానికి సబ్ట్రాక్టర్లను ఎక్కువగా ఉపయోగిస్తారు.

- ఇవి కూడా వర్తిస్తాయి వివిధ మైక్రోకంట్రోలర్లు అంకగణిత వ్యవకలనం, టైమర్లు మరియు ప్రోగ్రామ్ కౌంటర్ (పిసి) కోసం

- పట్టికలు, చిరునామాలు మొదలైనవాటిని లెక్కించడానికి ప్రాసెసర్లలో సబ్ట్రాక్టర్లను ఉపయోగిస్తారు.

- ఇది DSP మరియు నెట్వర్కింగ్ ఆధారిత వ్యవస్థలకు కూడా ఉపయోగపడుతుంది.

- సర్క్యూట్ యొక్క సంక్లిష్టతను తగ్గించడానికి గ్రాఫిక్స్ అనువర్తనాల కోసం CPU & GPU వంటి వ్యవకలనం కోసం కంప్యూటర్లలోని ALU కోసం ఇవి ప్రధానంగా ఉపయోగించబడతాయి.

- డిజిటల్ పరికరాల్లో వ్యవకలనం, కాలిక్యులేటర్లు మొదలైన అంకగణిత విధులను నిర్వహించడానికి ఇవి ప్రధానంగా ఉపయోగించబడతాయి.

- ఈ వ్యవకలనాలు టైమర్లు, పిసి (ప్రోగ్రామ్ కౌంటర్) & అంకగణిత వ్యవకలనం కోసం వివిధ మైక్రోకంట్రోలర్లకు కూడా తగినవి

- చిరునామాలు, పట్టికలు మొదలైనవాటిని లెక్కించడానికి ప్రాసెసర్ల కోసం వీటిని ఉపయోగిస్తారు.

- NAND & NOR వంటి లాజిక్ గేట్లతో దీనిని అమలు చేయడం పూర్తి సబ్ట్రాక్టర్ లాజిక్ సర్క్యూట్తో చేయవచ్చు ఎందుకంటే NOR & NAND గేట్లను రెండింటినీ యూనివర్సల్ గేట్స్ అంటారు.

పై సమాచారం నుండి, యాడెర్, రెండు సగం సబ్ట్రాక్టర్ సర్క్యూట్లను ఉపయోగించి పూర్తి సబ్ట్రాక్టర్ మరియు దాని పట్టిక రూపాలను అంచనా వేయడం ద్వారా, పూర్తి-సబ్ట్రాక్టర్లోని డౌట్ పూర్తి-యాడెర్ యొక్క సౌట్తో సమానంగా ఉంటుందని గమనించవచ్చు. పూర్తి వైవిధ్యం ఏమిటంటే A (ఇన్పుట్ వేరియబుల్) పూర్తి-వ్యవకలనంలో సంపూర్ణంగా ఉంటుంది. అందువల్ల, పూర్తి-యాడర్ సర్క్యూట్ను పూర్తి-వ్యవకలనంగా మార్చడం సాధించగలిగేది, అది ఇవ్వడానికి ముందు i / p A ని పూర్తి చేయడం ద్వారా లాజిక్ గేట్లు చివరి రుణ-బిట్ అవుట్పుట్ (బౌట్) ను ఉత్పత్తి చేయడానికి.

ఏదైనా పూర్తి సబ్ట్రాక్టర్ లాజిక్ సర్క్యూట్ను ఉపయోగించడం ద్వారా, NAND గేట్లను ఉపయోగించే పూర్తి సబ్ట్రాక్టర్ మరియు పూర్తి సబ్ట్రాక్టర్ ఉపయోగించి లేదా గేట్లను అమలు చేయవచ్చు, ఎందుకంటే NAND మరియు NOR గేట్లు రెండింటినీ సార్వత్రిక ద్వారాలుగా పరిగణిస్తారు. ఇక్కడ మీ కోసం ఒక ప్రశ్న ఉంది, సగం వ్యవకలనం మరియు పూర్తి వ్యవకలనం మధ్య తేడా ఏమిటి?